Revista Tecnológica ESPOL, Vol. xx, N. xx, pp-pp, (Mes, 200x)

# SIMULACION DE UN ESQUEMA DE UN ESQUEMA DE FEC (FORWARD ERROR CORRECTION) EN BASE AL ESTANDAR DVB (DIGITAL VIDEO BROADCASTING)

Jaime Armando Moscoso Alvarado (Tesista) Ing. Washington Medina (Director)

Fiec

Espol

Km. 30 ½ vía perimetral, Guayaquil, Ecuador.

amoscoso@espol.edu.ec (Tesista)

wmdeina@espol.edu.ec (director)

### Resumen

Las comunicaciones inalámbricas requieren el empleo de métodos de corrección de errores sobre los datos transmitidos, usándose generalmente técnicas de codificación Reed-Solomon & Viterbi, por razones de desempeño y seguridad es preferible implementarlos sobre hardware. En este trabajo se presenta el diseño modular de la etapa de codificación de estos códigos para su concatenación System Generator de Xilnx, orientado a la implementación sobre tecnología de matriz de compuertas programadas por campo (FPGA). Se inicia con una revisión de los conceptos asociados a la definición de los componentes, y el modelo, descripción del comportamiento, luego la arquitectura se realizó usando diseño basado en modelo. El esquema de FEC que se realizará se llevara a cabo acorde a las especificaciones del estándar DVB para televisión digital europeo.

Palabras Claves: Codificador, decodificador, Reed-Solomon, Viterbi, puncturing, interleaving.

#### Abstract

The wireless communication medium requires employing forward error correction methods on the data transferred, where Reed-Solomon & Viterbi coding techniques are generally utilized, because of performance and security reason. In this paper we present a modular design of phase encoding these codes for concatenation using System Generator of Xilinx and oriented to implementation with field programmable gate arrays (FPGA). The work begins with a review of code concept and the definition of the components and the model and the description of the behavioral. Later, the architecture is made based in model based design. The scheme of FEC will be done according to the specifications of the DVB standard for the digital Digital television.

### Introducción

En los procesos de transmisión de datos se deben emplear técnicas de codificación con corrección de error para garantizar la confiabilidad de la información. Entre las posibles soluciones para contrarrestar los efectos del canal pueden mencionarse algunas metodologías, como por ejemplo el uso de diversidad temporal, mediante códigos robustos, es decir, usando una cadena concatenada de códigos.

En la transmisión de señales de televisión digital en un medio urbano, el deterioro de la señal se produce por la infraestructura del sector, produciendo interferencias por multicamino, fading, etc. Todos estos problemas que se presentan alteran la señal haciendo que la señal de información en el receptor se corrompa y no pueda ser interpretada correctamente, El esquema de FEC sirve para proteger a la señal en lo posible de las adversidades del medio logrando una corrección en el receptor de los posibles errores generados en el canal.

Entre la codificación de canal [9,11], se presentan los esquemas empleados con mayor frecuencia, los cuales serán considerados con el objetivo de identificar los módulos a definir para realizar la descripción estructural.

En particular se revisan los códigos concatenados de forma serial compuestos por Reed-Solomon (como codificador externo) y códigos convolucionales (como codificador interno) y los intercaladores presentados en [2] para disminuir los errores por efecto ráfaga, siendo este esquema de codificación concatenado una alternativa eficiente, cuya ganancia se acerca al límite de Shannon, con respecto al empleo de los códigos de forma separada.

La concatenación entre códigos fue introducida por Forney como una técnica muy práctica para obtener un código de longitud suficientemente alta y una capacidad correctora extremadamente elevada. Eso se logra utilizando múltiples niveles de codificación, con el fin de lograr unas ganancias de codificación grandes, cercanas al límite de Shannon [3], por la combinación de dos códigos componentes relativamente simples. El esquema de codificación resultante es muy potente y está dotado de una estructura que permite una decodificación sencilla.

#### Bases teóricas

Una probabilidad de error muy baja puede obtenerse en el receptor gracias al efecto combinado de los dos códigos. En teoría, la concatenación en dos niveles no impide elegir cualquier pareja de códigos ni tampoco su posición dentro del esquema total.

La flexibilidad particular de un concepto de este tipo dejaría una libertad casi absoluta sobre la configuración que se puede elegir (Reed-Solomon & Viterbi). En la realidad, la configuración más utilizada es sobre dos niveles, porque ya con este tipo de concatenación, que es la más simple, se logran resultados más que suficientes para un número muy elevado de aplicaciones.

#### Codificador de Reed-Solomon

El codificador Reed-Solomon cuenta con un comportamiento definido en el campo de Galois; una palabra de código Reed-Solomon es generada usando un polinomio especial [2-3]. Todas las palabras de código válidas son divisibles exactamente por el polinomio generador.

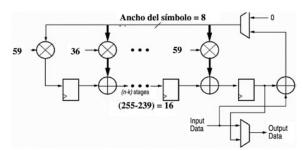

El diseño de un dispositivo para implementar un código Reed-Solomon RS(204,188,16) con símbolos de 8 bits, en el cual cada palabra de código contiene 204 bytes de palabra de código, de los cuales 188 bytes son datos y 16 bytes son paridad, con símbolos de 8 bits de longitud, consta de una serie de pasos.

Figura 1. Estructura del codificador RS(204,188,16).

Donde se observa cómo quedaría la arquitectura a configurar para tal aplicación donde la longitud de los registros de memoria será de 8 bits, se crearán 16 etapas para el RS(204,188,16) y se programarán las tabla que contienen la información de los productos en el campo de Galois para efectuar la operación entre los coeficientes y los datos de entrada.

### **Interleaving**

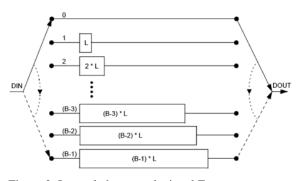

La técnica consiste en enviar al receptor réplicas independientes de la secuencia transmitida, transformando los errores correlacionados en errores aleatorios [7]. Más específicamente, consiste en eliminar la correlación entre

los datos en recepción. En sistemas concatenados, el entrelazado convolucional es necesario entre el codificador RS y el convolucional, porque la codificación RS trabaja mejor cuando los símbolos erróneos no están correlacionados. Sin el entrelazador o intercalador convolucional los símbolos erróneos tienden a correlacionarse y se agrupan en ráfagas producidas por el decodificador de Viterbi.

El principio de funcionamiento del intercalador convolucional de Forney consiste en un conjunto de retardos de línea estructurados a través de registros desplazamientos. Los símbolos de entrada serializados son distribuidos por medio de un multiplexor (conmutador) a cada una de las ramas del circuito, tal como se observa en la figura 2

Figura 2. Intercalador convolucional Forey.

### **Codificador Convolucional**

la inserción de k bits de redundancia asociado a la combinación de n bits consecutivos. Un codificador convolucional (n,k,K) para k entradas que ingresan a un circuito secuencial, con n salidas que se implementa a través de K niveles de memoria [1]. En el estándar DVB este codificador conserva los valores de (2,1,7) manteniendo un total de 6 registros. Y para cada ramal mantiene las conecciones 171oct y 133oct. Como se muestra en la figura 3.

Figura 3. Codificador convolucional de relación ½.

# rigara 3. Codificador convolacionar de

El Puncturing o perforado es la última etapa en el esquema de codificador de FEC. Esta última etapa es sólo un complemento del codificador convolucional, que como base tenía una tasa de codificación de ½ lo cual disminuye a la mitad la capacidad del canal [1].

El perforado, permite la supresión de ciertos bits ya codificados en la salida del codificador convolucional. El estándar propone que bits deben suprimirse, lo que indica en la tabla 1.

Tabla 1. Tabla de puncturing y tasas de código.

| Code Rates r | Puncturing pattern       | Transmitted sequence<br>(after parallel-to-serial conversion)                                                           |

|--------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1/2          | X: 1<br>Y: 1             | X <sub>1</sub> Y <sub>1</sub>                                                                                           |

| 2/3          | X: 1 0<br>Y: 1 1         | X <sub>1</sub> Y <sub>1</sub> Y <sub>2</sub>                                                                            |

| 3/4          | X: 101<br>Y: 110         | X <sub>1</sub> Y <sub>1</sub> Y <sub>2</sub> X <sub>3</sub>                                                             |

| 5/6          | X:10101<br>Y:11010       | X <sub>1</sub> Y <sub>1</sub> Y <sub>2</sub> X <sub>3</sub> Y <sub>4</sub> X <sub>5</sub>                               |

| 7/8          | X: 1000101<br>Y: 1111010 | X <sub>1</sub> Y <sub>1</sub> Y <sub>2</sub> Y <sub>3</sub> Y <sub>4</sub> X <sub>5</sub> Y <sub>6</sub> X <sub>7</sub> |

#### Desarrollo de la simulación

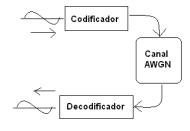

En la simulación en System Generator de las etapas anteriormente descritas se concatenan para lograr su codificación y son transmitidas por el canal de comunicación donde se corrompe la señal con ruido AWGN y luego se dirigen al receptor donde se decodifican obteniéndose la señal original a la entrada del codificador. El Programa System Generator pertenece a la marca Xilinx de FPGA's y este se soporta sobre Simulink de Matlab. El software presenta bloques similares a los de Simulink (diseño basado en modelo) con la diferencia que estos pueden ser programados sobre una FPGA.

Figura 4. Diagrama de bloques del Esquema de FEC.

En la figura 4 se aprecia un diagrama de bloques del simulador del esquema de FEC. Ese es el formato a implementar dentro del programa antes mencionado.

### **Puncturing**

#### Resultados

Una vez puesta en marcha la simulación se puede destacar la eficiencia del esquema de FEC con una comparación de la señal antes y después del canal, para visualizar la influencia del ruido en la señal.

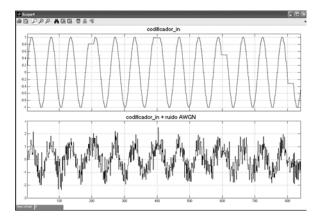

En la figura 5 se puede apreciar en la gráfica superior la señal a la entrada del codificador y en la parte inferior la misma señal luego de agregarle ruido AWGN con SNR=5 dB.

Figura 5. Señal sin codificar a la entrada (superior) y salida (inferior) del canal AWGN.

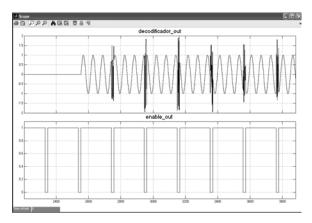

Se puede observar que hay un gran deterioro de la señal. En la parte superior de la figura 6 se muestra la señal decodificada en el receptor luego de haber atravesado el mismo canal AWGN con el mismo valor de SNR (5dB) que en la figura 5, con la diferencia que fue muestreada y codificada antes de su ingreso al canal de comunicaciones. En la parte inferior de la figura 6 se muestra la señal de enable, que indica la validez de la grafica en la parte superior.

Figura 6. Señal recibida luego de atravesar el canal AWGN (superior) con codificación, y señal enable (inferior).

Como se puede observar en la parte inferior de la figura 5 la señal sin codificar es vulnerable a todo el ruido del canal y demás adversidades, en cambio en la parte superior de la figura 6 se aprecia una señal más "limpia" y sin distorsiones pese a que atravesaron el mismo canal bajo las mismas condiciones.

#### **Conclusiones**

Los módulos programados permiten codificar y decodificar respectivamente los datos para aplicaciones en sistemas de comunicación, ofreciendo alto nivel de paralelismo en el procesamiento a través de hardware, lo que se traduce en una reducción del tiempo de procesamiento.

Estos diseños pueden ser programados en System Generator de Xilinx y ser sintetizados en un FPGA, lo que permite diseños "Sistemas sobre Chip" donde múltiples módulos pueden ser combinados en un solo circuito integrado [3].

El análisis matemático es un excelente complemento didáctico para la enseñanza de la teoría de las comunicaciones digitales, ya que al emplear este tipo de fundamentos logra consolidar la comprensión de los conceptos básicos y las características principales de los códigos.

La característica principal de este esquema de FEC es la unión de estos dos tipos de codificación (interna y externa), pues el decodificador interno reconstruye la señal aproximando la señal recibida a la más cercana de las posibles correctas (Algoritmo de Viterbi). Este proceso "limpia" la señal y descarta gran parte de los errores, dejándole un trabajo menos riguroso al decodificador externo.

### Referencias

- [1] C.E. Shannon. "A Mathematical Theory of Communication". Bell System Technical Journal. Vol. 27, pp. 379-423. 1948.

- [2] I.S. Reed-Solomon. "Polynomial Codes over Certain Finite Fields". Journal of the Society for Industrial and Applied Mathematics. Vol. 8 N° 2, pp. 300-304. 1960.

- [3] Xilinx Blockset Reference Guide. Xilinx System Generator v2.1 for Simulink. 2007.

- [4] IEEE802-Compatible Viterbi Decoder v1.1, 2004.

- [5] "Digilab DIO2 Reference Manual". 2002. URLs:

www.digilentinc.com

- [6] A. Agatep. "Reed-Solomon Solutions with Spartan-II FPGA". WP110 (v1.1). February 10, 2000.

- [7] A. Agatep. "Reed-Solomon Solutions with Spartan- II FPGA". WP110 (v1.1). February 10, 2000.

- [8] Ulloa V., Fernando. "Contribución al estudio de un modelo de canal aeronáutico para sistemas de radiocomunicación digital terrestre basados en plataformas estratosféricas HAPS". Tesis para optar al grado de doctor. Barcelona, España. 2003.

- [9] A. Arriagada. "FEC (Forward Error Correction) y Código Reed-Solomon". Universidad de Concepción. Concepción, Chile. 2001.