### ESCUELA SUPERIOR POLITÉCNICA DEL LITORAL CENTRO DE INVESTIGACIÓN CIENTÍFICA Y TECNOLÓGICA

"Diseño y simulación del control de un transformador de estado sólido de tres etapas con entrada monofásica y salida monofásica basado en un convertidor DC-DC de doble puente activo y un convertidor AC-DC multinivel de diodo anclado."

Contreras Gregorio<sup>1</sup>, Valle Carlos<sup>2</sup>, Dr. Síxifo Falcones<sup>3</sup>

Facultad de Ingeniería en Electricidad y Computación Escuela Superior Politécnica del Litoral (ESPOL)

Campus Gustavo Galindo, Km 30.5 vía Perimetral

Apartado 09-01-5863. Guayaquil – Ecuador

gcontrethierry@hotmail.com<sup>1</sup>, carlosandresvallevillamarin@gmail.com<sup>2</sup>, sixifo@espol.edu.ec<sup>3</sup>

#### Resumen

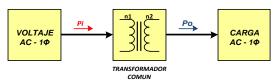

Este proyecto presenta el diseño y control de un transformador de estado sólido (SST). Una de las principales funciones del SST es la capacidad de integrarse a fuentes de energía alternativa, esto en caso de que la alimentación principal se desconecte, y por medio de otra fuente de energía seguir alimentando a la carga y permitir el flujo de potencia a la red, manteniendo las magnitudes en los valores establecidos y ofreciendo estabilidad al sistema ante la presencia de perturbaciones comunes en un sistema de potencia, mejorando la calidad de la energía eléctrica.

El SST diseñado trabaja con entrada y salida monofásica, consta de tres etapas que son: Rectificador, DAB e Inversor, se dimensiona los elementos que lo componen y se realiza el control de los parámetros eléctricos en las diferentes etapas. Para comprobar su correcto funcionamiento se realizan pruebas de: Sag & Swell, presencia de armónicos, sobrecarga, bajo factor de potencia e inyección de potencia DC en el enlace de baja.

El trabajo se lo realiza con la ayuda de las herramientas PLECS y SIMULINK, del programa MATLAB, en el cual se simula el sistema modelado.

Palabras Claves: Transformador de Estado Sólido, SST, Convertidores Multinivel, Diodo Anclado.

#### **Abstract**

This project presents the design and control of a solid state transformer (SST). One of the main functions of SST is the ability to integrate alternative energy sources, in case the SST get disconnected of the main power, and through other energy source to continue to feed the load and allow the flow of power to the network, keeping it parameters in the set values and providing stability to the system within presence of disturbances in a power system, improving the power quality.

The SST was designed to work with a single-phase input and output, consists of three stages which are: Rectifier, DAB and Inverter. All the elements are sized and control of electrical parameters is performed at each one of different stages. To verify the correct operation of the SST, some tests are performed (Sag & Swell, presence of harmonics, overload, low power factor and DC power injection in the LVDC link). The work is done using SIMULINK, PLECS and MATLAB, to simulate the designed system.

Keywords: Solid State Transformer, SST, Multilevel Converters, Clamped Diode.

#### 1. Introducción.

Debido al incremento en la demanda de la energía eléctrica surge la necesidad del desarrollo de nuevas tecnologías, para optimizar la calidad de energía de un sistema eléctrico de potencia, y que además permitan la inclusión de energías renovables a través de la generación distribuida.

La energía eléctrica antes de llegar a los consumidores debe pasar por las etapas de generación, transmisión y distribución. El elemento principal para llevar a cabo estos procesos es el transformador eléctrico, este dispositivo sirve únicamente para aumentar o disminuir niveles de tensión o de corriente, con un alto nivel de eficiencia [1].

La mayoría de los problemas son ocasionados en la parte de distribución en donde el transformador eléctrico no permite: integrarse a fuentes de energía alternativa, monitorear cargas y flujo de potencia bidireccional. En la Figura 1. se muestra el papel principal del transformador eléctrico.

**Figura 1.** Distribución de energía usando un transformador eléctrico.

En consecuencia a esto es necesario conocer los problemas más frecuentes que afectan el rendimiento de los equipos que se utilizan en los sectores industriales, en nuestro hogar, o comerciales, entre los más comunes tenemos: Picos de voltaje, Bajas de voltaje, Sobre-Voltajes, Apagones y la Distorsión Armónica [2].

Lo que se propone es utilizar la red eléctrica inteligente donde para mejorar la calidad y capacidad del suministro de energía eléctrica se diseña el transformador de estado sólido o SST [3].

Figura 2. Distribución de energía implementado un SST.

### 2. Fundamento Teórico

# 2.1 Transformador de Estado Sólido (SST).

Un transformador de estado sólido (SST) es un conjunto de componentes semiconductores de alta potencia, transformadores de alta frecuencia convencionales y sus respectivos circuitos de control. Se utiliza para proporcionar un alto nivel de confiabilidad en el control para un red de distribución de energía, incorporando también una cierta capacidad de comunicación al sistema convirtiéndola así en una red inteligente o Smart Grid [4].

# 2.1.1 Características del Transformador de Estado Sólido

El transformador de estado sólido (SST) puede incrementar o reducir los niveles de voltaje AC al igual que la del transformador tradicional, pero adicionalmente ofrece una serie de ventajas importantes [4]. Estas incluyen:

- Permitir el flujo bidireccional de la energía eléctrica.

- Puede ser conectado directamente a la red de distribución.

- Puede ser conectado a una fuente DC o una fuente de energía alternativa como generadores fotovoltaicos o eólicos favoreciendo el incremento de generación distribuida en sectores alejados a la red.

- La entrada o salida de corriente alterna (AC) o continua (DC).

- Cambiar activamente las características de potencia, tales como los niveles de tensión y frecuencia.

- Mejorar la calidad de la energía (compensación de energía reactiva y filtrado de armónicos).

- Reducir en gran medida el tamaño físico y el peso de los componentes individuales de transformadores con potencias equivalentes.

# 2.1.2 Topologías del Transformador de Estado Sólido.

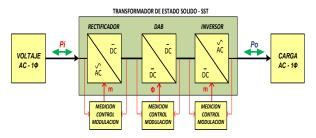

En la figura 3 a continuación, se muestran 4 distintas topologías con las que se puede implementar un SST para obtener un flujo de potencia bidireccional [5].

**Figura 3.** Topologías de un Transformador de Estado Sólido.

- a) Transformador de estado sólido de una etapa.

- b) Transformador de estado sólido de dos etapas con enlace DC de Baja tensión.

- c) Transformador de estado sólido de dos etapas con enlace DC de Alta tensión.

- d) Transformador de estado sólido de tres etapas con enlace DC de Baja y Alta tensión.

### 2.2 Convertidores Multinivel

Los Convertidores Multinivel presentan un amplio conjunto de semiconductores de potencia y fuentes de tensión basadas en condensadores. Con un adecuado control de la conmutación de los interruptores es posible generar tensiones de salida elevadas y con formas de onda escalonadas, considerando que los interruptores se cierran y abren en tiempos diferentes, dependiendo del número de interruptores de potencia, la tensión en la salida crece sumando las tensiones parciales en los condensadores, mientras que los semiconductores sólo soportan los niveles de tensión de entrada [6].

### 2.2.1 Convertidor Multinivel con Diodo Anclado (Clamped – Diode Converter)

Su función principal es sintetizar una onda sinusoidal a partir de varios niveles de tensión, normalmente obtenida de condensadores que funcionan como fuentes DC. Los condensadores utilizados se conectan en serie para dividir la tensión y de esta manera, los dispositivos de potencia operan con una tensión menor entre terminales.

En esta configuración la tensión en el bus de continua se divide en n niveles, y el número de condensadores sería (n-1), donde la tensión DC total en el bus se divide con un adecuado control en la conmutación, en tensiones parciales iguales para cada condensador existente en el bus de continua.

Basándose en el número de niveles del convertidor, en cada ramal se van a requerir 2(n-1) interruptores de potencia y 2(n-2) diodos fijadores. Los diodos conectados en el circuito tienen como función anclar (clamp) las tensiones de bloqueo de los interruptores a una fracción de la tensión en el bus de continua [7].

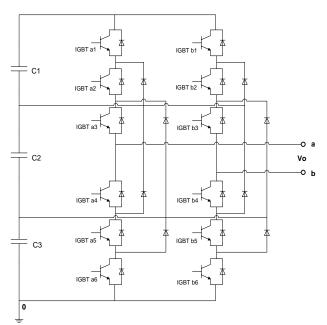

El circuito de la figura 4 se puede analizar considerando el punto de salida a y el nodo de referencia en el bus de continua 0. La tensión de fase Va puede tomar 4 niveles de tensión diferente: +VDC, +2/3VDC, +1/3VDC y 0V por cada fase. La tensión de salida Vo está formado por la fase positiva a y la fase negativa b, por lo que cada fase constituye un semi-ciclo de la señal sinusoidal.

**Figura 4.** Diagrama de circuito de un convertidor de 4 niveles con diodo anclado (Clamped-Diode).

#### 2.2.2 Modulación Multinivel.

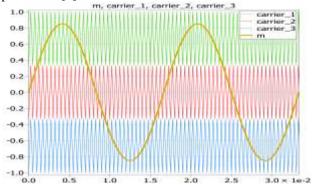

La modulación multinivel es la base para la obtención de una onda de voltaje que muestre una buena calidad en su forma, es decir; que sea una señal sinusoidal casi perfecta con un rizado mínimo producto de los armónicos inherentes de la conmutación. Dependiendo del número de niveles que se utilice se aporta significativamente a la disminución del rizado [8].

El proceso de modulación es similar a la modulación de ancho de pulso ya que se realiza una comparación entre una señal sinusoidal (moduladora) y varias señales triangulares (portadoras), en la figura 4 se muestra el proceso de modulación mediante la señal moduladora y portadoras [9]

Figura 5. Señal moduladora y 3 señales portadoras.

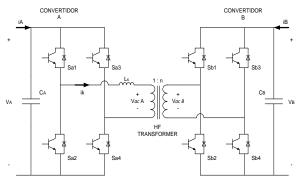

### 2.3 Dual Active Bridge (DAB).

Es una topología de Convertidor DC con aislamiento en la cual los dos convertidores en ambos lados del aislamiento del transformador son DC-AC bidireccionales de puente completo y su control es realizado en base a la técnica de modulación por desplazamiento de fase (PSM). La configuración de los interruptores los obliga a operar en pares de conmutación diagonales en cada convertidor que se encienden simultáneamente con el 50% de ciclo de trabajo y con 180 grados de desfase entre los dos ramales de cada convertidor para proporcionar una onda de voltaje AC casi cuadrada en los terminales del transformador. El desplazamiento de fase entre las dos tensiones de corriente alterna, denotado por la variable  $\phi$ , es un parámetro importante que determina la dirección y la cantidad de potencia eléctrica transferida entre los buses de corriente continua. Al ajustar este desfase, una operación de frecuencia fija con el control total de la transferencia de energía es posible [10].

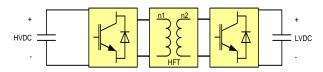

**Figura 6.** Diagrama de un Convertidor "Dual Active Bridge".

La potencia promedio transferida puede obtenerse mediante el cálculo de la potencia media de corriente alterna en los terminales del transformador.

$$P = \frac{1}{2\pi} \int_0^{2\pi} (V_{ac} A \cdot i_K) d\omega t \tag{1}$$

$$P = \frac{V_A V_B}{n L_K \omega} \emptyset \left( 1 - \frac{|\emptyset|}{\pi} \right)$$

(2)

donde  $L_K$  es la inductancia de fuga del transformador, n es la relación de vueltas del transformador y  $\omega$  es la frecuencia en radianes. Si se desea una transferencia de energía del lado A al lado B,  $V_{ac}A$  debe adelantar a  $V_{ac}B$  y el ángulo  $\phi$  debe ser considerado positivo. Si se desea una transferencia de energía del lado A al lado B,  $V_{ac}A$  debe retrasar a  $V_{ac}B$  y el ángulo  $\phi$  debe ser considerado negativo [10].

## 3. Dimensionamiento de los Componentes del SST.

Para el dimensionamiento del SST se consideran los siguientes valores nominales:

| significes valores nonlineares.         |               |

|-----------------------------------------|---------------|

| Magnitud                                | Valor Nominal |

| Voltaje monofásico de entrada           | 13470 [V]     |

| Voltaje monofásico de salida            | 110 [V]       |

| Carga monofásica conectada al SST       | 100 [Kva]     |

| Índice de modulación para los 3 bloques | 0.8           |

| <b>= 11 4 = '0'</b> '                   | 1 1 0 O T     |

Tabla 1. Especificaciones del SST.

## 3.1 Dimensionamiento de los Componentes del Rectificador.

El bloque rectificador constituye la primera etapa del SST, aquí el voltaje AC de la fuente es convertido en voltaje DC, trabaja con un voltaje nominal de 7620 [V], y tiene la capacidad de entregar 100 [Kva] de potencia, que será la potencia nominal de la carga a ser conectada.

| Magnitud                                        | Valor<br>nominal |

|-------------------------------------------------|------------------|

| Voltaje RMS en la red                           | 7620 [V]         |

| Corriente RMS en la red                         | 13.2 [A]         |

| Frecuencia de conmutación                       | 20 [KHz]         |

| Voltaje DC - link                               | 13470 [V]        |

| Porcentaje de Rizado de la<br>Corriente AC-pico | 3%               |

| Porcentaje de Rizado del                        | 1 %              |

Tabla 2. Especificaciones del Rectificador.

Voltaje DC - pico

El diseño del inductor se realiza considerando la variación de la corriente para controlar el rizado de la señal de corriente, que debe ser de 3%, con el sistema trabajando a carga nominal.

Se determina la variación máxima de voltaje, y se procede a obtener el valor del inductor mediante las ecuaciones:

$$I_{L_{\text{nom}}} = \frac{100000 \text{ [VA]}}{7620 \text{ [V]}} * \sqrt{2} = 18.557 \text{[A]}$$

(3)

$$\Delta I_{L} = 3\% * I_{L_{\text{nom}}} = 0.556776 \tag{4}$$

$$L_{HVDC} = \frac{\int V_L dt}{\Delta I_L}$$

(5)

con estos valores se obtiene el valor del inductor,  $L_{HVDC} = 194.7581 [mH]$ . Luego se establece el ángulo fase de operación del rectificador aplicando las ecuaciones de flujo de potencia:

$$\emptyset = \sin^{-1}\left(\frac{100000 \, [VA] \times 73.42207 \, [\Omega]}{(7620 \, [V])^2}\right) = 7.2644^{\circ} \tag{6}$$

Cada bloque rectificador entrega el mismo voltaje DC, correspondiente a un tercio del voltaje DC total que se espera, es decir un valor nominal de 4491 [V]. A continuación se obtienen los capacitores, basándose en la frecuencia de la red  $\omega_g$ ,  $S_{max}$  es la potencia compleja máxima que entrega el capacitor [11].

$$C = \frac{S_{\text{max}}}{2*\omega_g * V_{\text{dc}}^n * V_{\text{dc}rpp}} \tag{7}$$

El valor de cada capacitor es dado en la siguiente tabla:

| Capacitor | Valor Calculado |

|-----------|-----------------|

| CHVDC1    | 220.9409 [uf]   |

| CHVDC2    | 467.2913 [uf]   |

| CHVDC3    | 220.9409 [uf]   |

Tabla 3. Capacitores en el Enlace HVDC.

## 3.2 Dimensionamiento de los Componentes del DAB.

El DAB se encarga de transformar el voltaje que recibe el SST. Este bloque recibe una señal DC y por medio de un convertidor la transforma en una señal AC de alta frecuencia y un transformador es el encargado de reducir el voltaje para luego transformar la señal en una señal DC. El SST va a estar compuesto por tres DAB que reciben la señal DC de los capacitores del bloque anterior.

| Magnitud                  | Valor nominal |

|---------------------------|---------------|

| Voltaje DC entrada        | 4491 [V]      |

| Voltaje DC salida         | 388.91 [V]    |

| Frecuencia de conmutación | 20 [KHz]      |

Tabla 4. Especificaciones para cada DAB.

Se considera un transformador ideal, con un núcleo hecho de un material con baja autoinducción magnética, lo que permite trabajar en régimen de alta frecuencia, la relación de vueltas entre el devanado primario y secundario está dada por la expresión:

$$\frac{n_1}{n_2} = \frac{4491[V]}{388.91[V]} = \frac{11.54}{1} \tag{8}$$

Para el dimensionamiento del inductor de este convertidor se utiliza la siguiente ecuación [10]:

$$P_{DAB} = \frac{V_A V_B}{2\pi * 60 * L_{DAB}} \emptyset_{Nom} \left( 1 - \frac{|\emptyset_{Nom}|}{\pi} \right); \ \emptyset_{Nom} = \frac{7\pi}{36}$$

(9)

| $L_{DAB} = \frac{V_A \times V_B}{2\pi \times f_c \times P_{DAB}} \times \emptyset_{Nom}$ | $\left(1-\frac{ \emptyset_{\text{Nom}} }{\pi}\right)$ | (10) |

|------------------------------------------------------------------------------------------|-------------------------------------------------------|------|

| ZTIXICXPDAD                                                                              | \ π /                                                 |      |

| Inductor | Valor Calculado |

|----------|-----------------|

| L_dab1   | 1.638 [mf]      |

| L_dab2   | 0.7669 [mf]     |

| L_dab3   | 1.638 [mf]      |

Tabla 5. Inductores a usar en cada DAB.

Se obtiene el capacitor, basada en la frecuencia de la red  $\omega_g$ ,  $S_{max}$  es la potencia compleja máxima que entrega el capacitor [11].

$$C = \frac{S_{max}}{2*\omega_g*V_{dc}^n*Vdc_{rpp}} \tag{11}$$

| Capacitor | Valor Calculado |

|-----------|-----------------|

| CLVDC     | 138.4192 [mf]   |

Tabla 6. Capacitor del Enlace DC de baja.

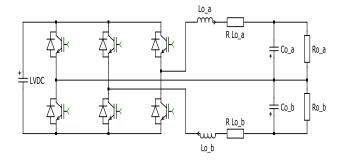

## 3.3 Dimensionamiento de los Componentes del Inversor.

Figura 7. Esquema del Bloque Inversor del SST.

Para calcular los componentes del inversor se debe tener en cuenta las siguientes especificaciones:

| Magnitud                                     | Valor Nominal |

|----------------------------------------------|---------------|

| Voltaje RMS en la red, V <sub>g</sub>        | 110[V]        |

| Corriente Pico en la red, $I_{ m g}^{ m pk}$ | 642.82 [A]    |

| Frecuencia de Conmutación, f <sub>s</sub>    | 20 [KHz]      |

| Voltaje DC-Link, V <sub>dc</sub>             | 388.91 [V]    |

| Porcentaje de Rizado de Corriente AC<br>Pico | 3%            |

| Porcentaje de Rizado de Voltaje DC<br>Pico   | 1%            |

Tabla 7. Especificaciones del Bloque Inversor.

$$I_{g}^{pk} = \frac{100000 \, [VA]}{110 \, [V]} * \sqrt{2} = 642.82 [A]$$

(12)

$$\Delta I_g^{pk} = 3\% * I_g^{pk} = 19.2847 \tag{13}$$

$$L_{\rm inv} = \frac{\int V_{\rm L} dt}{\Delta I_{p}^{\rm pk}} \tag{14}$$

Con estas expresiones se obtiene el valor del inductor,  $L_{inv} = 201.665 [\mu H]$ , este es el valor del inductor para la *Fase A* pero debido a que se trabaja con circuito simétrico será el mismo valor para la *Fase B*.

Para determinar el valor del capacitor, se utiliza el método de ajuste de la frecuencia de resonancia entre el inductor y el capacitor del filtro LC. La frecuencia de resonancia establecida tiene que ser una década menor a la frecuencia de conmutación que es 20 [KHz], por lo que la frecuencia de resonancia será  $f_{\rm res} = 2$  [KHz]. La fórmula para hallar el valor del capacitor está dada por la ecuación:

$$f_{\text{res}} = \frac{1}{2\pi \times \sqrt{L \times C}}$$

(15)

Se despeja C de la ecuación anterior y se obtiene el valor de los capacitores para el inversor.

$$C = \frac{1}{L} \times \left(\frac{1}{2\pi \times f_{\text{res}}}\right)^2 = 31.4014 \,[\mu f] \tag{16}$$

Este es el valor del capacitor para la *Fase A* pero debido a que se trabaja con circuito simétrico será el mismo valor para la *Fase B*.

### 4. Diseño del controlador del SST.

### 4.1 Estrategia de Control.

- Dividir al SST en 3 etapas y obtener el modelo matemático (función de transferencia) de cada etapa.

- Los voltajes que se deberán controlar son:

- ✓ Voltaje total en el Enlace DC de Alta tensión.

- ✓ Voltaje parcial en cada Condensador del Enlace DC de Alta tensión.

- ✓ Voltaje del Enlace DC de Baja Tensión.

- ✓ Voltaje de cada fase en la salida del SST.

- En cuanto a las corrientes, se diseñarán controladores para la corriente que entra al SST desde la red y para las corrientes de salida por fase del SST.

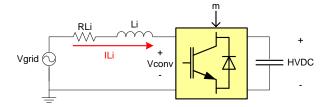

# 4.2 Modelo Matemático de la Etapa AC-DC (Rectificador).

Para realizar el diseño del controlador de la Etapa AC-DC, se deben primero obtener las ecuaciones del modelo matemático de esta etapa.

Figura 8. Diagrama del circuito de la Etapa Rectificadora del SST.

$$V_{\text{grid}} - V_{\text{RLi}} - V_{\text{Li}} - V_{\text{conv}} = 0 \tag{17}$$

$$V_{grid} - V_{conv} - I_{Li} R_{Li} - L_i \frac{dI_{Li}}{dt} = 0$$

(18)

Se llevará esta ecuación al dominio de la frecuencia utilizando la Transformada de Laplace:

$$V_{conv} - I_{Li}(SL_i + R_{Li}) = 0$$

;  $V_{conv} = mHVDC$  (19)

$$G_{pi}(s) = \frac{I_{Li}}{m} = -\frac{HVDC}{SL_i + R_{Li}}$$

(20)

Para obtener la ganancia de la planta de voltaje se plantean las ecuaciones de la energía en el Enlace DC de Alta.

$$E(t) = \int (P_{conv} - P_o)dt \tag{21}$$

$$E = \frac{1}{s} P_{conv} \quad ; \quad P_{conv} = \frac{V_{grid_{pk}} I_{Li_{pk}}}{2}$$

(22)

$$G_{pv}(s) = \frac{E}{I_{Li_{pk}}} = \frac{V_{grid_{pk}}}{2s}$$

(23)

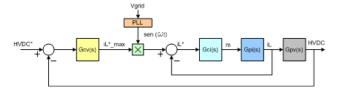

El método que se utilizará para realizar el control de lazo cerrado en esta etapa del SST será de control en cascada, en donde se tiene dos controladores, uno interno que se encargará de controlar la corriente de entrada, y otro externo que se encargará de realizar el control del voltaje en el Enlace DC. Para que este método de control funcione adecuadamente es necesario que el lazo interno tenga una respuesta mucho más rápida que el lazo externo, es decir que se estabilice antes que este.

Figura 9. Esquema de control de la etapa AC-DC.

Para el cálculo del controlador se utilizará el Método de Aproximación del Factor K, que permite hallar polos y ceros para un valor de Margen de Fase y Frecuencia de Corte determinados, con lo cual se podrá diseñar el controlador correctamente [12].

Existen tres tipos de controladores que se presentan en la siguiente tabla:

| Tipo | Ganancia                                                                                                     | Condición             |

|------|--------------------------------------------------------------------------------------------------------------|-----------------------|

| I    | $G_c(s) = \frac{k_c}{s}$                                                                                     |                       |

| II   | $G_c(s) = \frac{k_c}{s} \frac{\left(1 + \frac{s}{\omega_z}\right)}{\left(1 + \frac{s}{\omega_p}\right)}$     | $\omega_z < \omega_p$ |

| III  | $G_c(s) = \frac{k_c}{s} \frac{\left(1 + \frac{s}{\omega_z}\right)^2}{\left(1 + \frac{s}{\omega_p}\right)^2}$ | $\omega_z < \omega_p$ |

**Tabla 8.** Ganancias de los diferentes tipos de controladores utilizando el Método de aproximación del Factor K [12].

| Ø <sub>boost</sub> Requerido | Tipo de Controlador |

|------------------------------|---------------------|

| 00                           | Tipo I              |

| <90°                         | Tipo II             |

| >90°                         | Tipo III            |

**Tabla 9.** Selección de tipo de controlador según requerimiento de fase [12].

$$\emptyset_{\text{boost}} = 60^{\circ} - (-89.97^{\circ}) - 90^{\circ} = 59.97^{\circ}$$

(24)

$$k = \tan\left(\frac{\phi_{\text{boost}}}{2} + 45^{\circ}\right) \tag{25}$$

$$\omega_z = \frac{\omega_c}{k} \hspace{0.5cm} ; \hspace{0.5cm} \omega_p = k\omega_c \hspace{0.5cm} (26)$$

$$G_{c}(s) = -\frac{k_{c}}{s} \frac{\left(1 + \frac{s}{16849.52}\right)}{\left(1 + \frac{s}{234299.98}\right)}$$

(27)

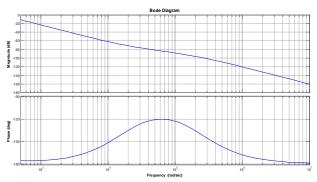

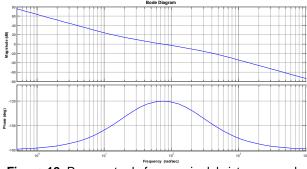

Figura 10. Respuesta de frecuencia de la planta de corriente de la Etapa AC-DC, incluyendo la ganancia del controlador con kc =1.

Se observa que la gráfica de magnitud tenga ganancia 0 dB al valor de la frecuencia de corte establecida, si es que no llega a suceder esto, se obtendrá la ganancia que se tiene a la frecuencia de corte del sistema y se divide para uno [12].

$$dB = 20\log G \tag{28}$$

$$Kc = \frac{1}{G} \tag{29}$$

Y la ganancia completa del controlador calculado será:

$$G_{c}(s) = -\frac{0.000065507}{s} \frac{\left(1 + \frac{s}{16849.52}\right)}{\left(1 + \frac{s}{234299.98}\right)}$$

(30)

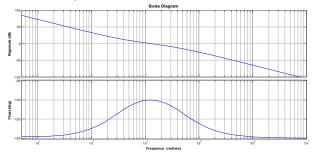

Se realiza de nuevo el diagrama de bode del sistema incluyendo al controlador, se podrá comprobar que cumple con las especificaciones planteadas (ancho de banda y margen de fase deseados).

**Figura 11.** Respuesta de frecuencia del sistema para la planta de corriente de la Etapa AC-DC, incluyendo el controlador.

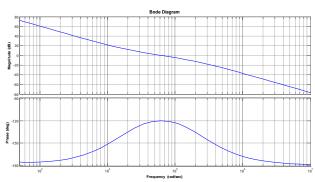

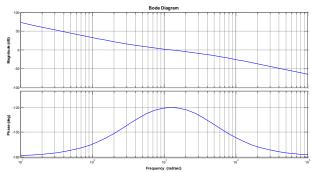

Para el controlador de la planta de voltaje se utilizará el mismo método que se utilizó para el diseño del controlador anterior, es decir el diseño del controlador por el Método de Aproximación del Factor k.

La frecuencia de corte requerida para el controlador es de 12 Hz siendo menor que la frecuencia de conmutación del convertidor 20 kHz. Ya que la corriente que entra al capacitor tiene una frecuencia natural propia de 120 Hz, se eligió una frecuencia de corte una década antes. Por lo tanto la ganancia completa del controlador calculado será:

$$G_{c}(s) = \frac{0.283}{s} \frac{\left(1 + \frac{s}{20.203}\right)}{\left(1 + \frac{s}{281.386}\right)}$$

(31)

Se realiza el diagrama de bode del sistema incluyendo al controlador para comprobar que cumple con las especificaciones planteadas (ancho de banda y margen de fase deseados).

**Figura 12.** Respuesta de frecuencia del sistema para la planta de voltaje de la Etapa AC-DC, incluyendo el controlador.

# 4.3 Modelo Matemático de la Etapa DC-DC (DAB).

Figura 13. Diagrama para los DAB en la Etapa DC-DC del

Para obtener la ganancia del sistema primero se describe la ecuación de la potencia en el DAB:

$$P_{DAB} = \frac{HVDC'LVDC}{XL'_{DAB}} \emptyset \left( 1 - \frac{\emptyset}{\pi} \right)$$

(32)

$$\Delta P_{\rm DAB} = \frac{\partial P_{\rm DAB}}{\partial \phi} \Big|_{\phi = 0} \Delta \phi \tag{33}$$

$$\frac{\Delta P_{\rm DAB}}{\Delta \emptyset} = \frac{HVDC'LVDC}{XL'_{\rm DAB}} \left( 1 - \frac{2\emptyset}{\pi} \right) \Big|_{\emptyset = 0}$$

(34)

$$\frac{P_{DAB}}{\emptyset} = \frac{HVDC'LVDC}{XL'_{DAB}}$$

(35)

Luego se debe analizar la energía en el condensador del Enlace DC de alta tensión.

$$E_{HVDC} = \int (P_i - P_{DAB})dt \tag{36}$$

$$E_{HVDC} = -\frac{1}{s} P_{DAB} \tag{37}$$

$$G_{\text{DAB}_{1,3}} = \frac{P_{\text{DAB}}}{\emptyset} * \frac{E_{\text{HVDC}}}{P_{\text{DAB}}} = -\frac{1}{s} \frac{\text{HVDC'LVDC}}{\text{XL'}_{\text{DAB}}}$$

(38)

La ecuación de la energía en el condensador del enlace DC de baja tensión para el DAB 2 es diferente al caso anterior.

$$E_{LVDC} = \int (P_{DAB} - P_o)dt$$

(39)

$$E_{LVDC} = \frac{1}{s} P_{DAB} \tag{40}$$

$$G_{DAB_2} = \frac{P_{DAB}}{\emptyset} * \frac{E_{LVDC}}{P_{DAB}} = \frac{1}{s} \frac{HVDC \ LVDC'}{XL_{DAB}} \tag{41}$$

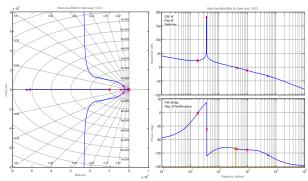

Una vez obtenida la ganancia del sistema se calcula la ganancia de los controladores de los voltajes parciales en los condensadores 1 y 3 del enlace DC en AT mediante el método de aproximación del factor k, con un Margen de fase de MF=60°, y una frecuencia de corte de 66.67 Hz.

$$G_{c}(s) = -\frac{0.16}{s} \frac{\left(1 + \frac{s}{112.2383}\right)}{\left(1 + \frac{s}{1563.3}\right)}$$

(42)

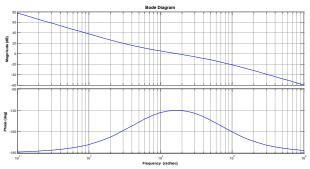

Se realiza el diagrama de bode del sistema incluyendo la ganancia del controlador para comprobar que cumple con las especificaciones planteadas (ancho de banda y margen de fase deseados).

Figura 14. Respuesta de frecuencia del sistema de los DAB 1 y 3, incluyendo la ganancia del controlador.

Luego se calcula la ganancia del controlador de voltaje en el Enlace DC de BT mediante el método de aproximación del factor k, con un Margen de fase de MF=60°, y una frecuencia de corte de 80 Hz.

$$G_{c}(s) = \frac{0.3237 \frac{\left(1 + \frac{s}{134.686}\right)}{2 \left(1 + \frac{s}{1875.9}\right)}$$

(43)

Figura 15. Respuesta de frecuencia del sistema del DAB 2 en la Etapa DC-DC, incluyendo la ganancia del controlador.

# 6.6 Modelo Matemático de la Etapa DC-AC (Inversor).

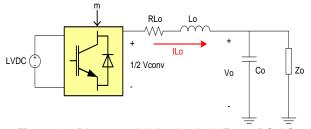

Figura 16. Diagrama del circuito de la Etapa DC-AC.

Aplicando la Ley de Voltajes de Kirchhoff se obtiene la siguiente ecuación:

$$0.5V_{conv} - V_{RL_o} - V_{L_o} - V_o = 0 (44)$$

$$0.5 \text{mLVDC} - I_{L_o} RL_o - L_o \frac{dI_{L_o}}{dt} - V_o = 0$$

(45)

Se lleva la ecuación al dominio de la frecuencia utilizando la transformada de Laplace:

$$0.5 \text{mLVDC} - I_{L_0} (sL_0 + RL_0) - V_0 = 0$$

(46)

Se descarta el efecto de Vo y se tiene la ganancia del sistema de la planta de corriente del inversor:

$$G_{pi}(s) = \frac{I_{L_0}}{m} = \frac{0.5 * LVDC}{(sL_0 + RL_0)}$$

(47)

Una vez modelada la planta de corriente de la etapa inversora, se puede decir que para la planta de voltaje la corriente  $I_{Lo}$  es una constante, por lo que se considerará al convertidor como una fuente de corriente AC.

$$I_{L} = I_{C} + I_{o} \tag{48}$$

$$I_{L} = C \frac{dV_{o}}{dt} + \frac{V_{o}}{Z_{o}} \tag{49}$$

Se lleva la ecuación al dominio de la frecuencia usando la transformada de Laplace:

$$I_{L} = V_{o} \left( sC + \frac{1}{Z_{o}} \right) \tag{50}$$

La ganancia del sistema para la planta de voltaje será:

$$G_{pv}(s) = \frac{V_0}{I_L} = \frac{Z_0}{sCZ_0 + 1}$$

(51)

Para esta etapa los parámetros a controlarse serán aquellos que el SST entregue a la carga. Se utilizará el método de controlador en cascada, el lazo interno se encargará de realizar el control de la corriente y el lazo externo controlará el voltaje en la salida del convertidor. Como el convertidor utilizado para esta etapa del SST es de fase partida, se considerará cada fase como un sistema individual y las dos fases serán consideradas idénticas por lo cual será suficiente diseñar el controlador para una de las fases ya que para la otra se utilizará el mismo.

Una vez obtenida la ganancia del sistema para la planta de corriente se calcula la ganancia del controlador por medio del método del factor k, con frecuencia de corte de 2000 Hz y margen de fase de 60°. Por lo tanto la ganancia del controlador será:

$$G_{c}(s) = \frac{43.8992 \left(1 + \frac{s}{3368.5}\right)}{s \left(1 + \frac{s}{46999}\right)}$$

(52)

Se realiza el diagrama de bode incluyendo la ganancia del controlador, para comprobar que cumple con las especificaciones planteadas (ancho de banda y margen de fase deseados).

Figura 17. Respuesta de frecuencia para la planta de corriente de la Etapa DC-AC del SST, incluyendo la ganancia del controlador.

Para el diseño del controlador de la planta de voltaje del inversor se utilizará el método de polo resonante, que consiste en agregar un polo resonante en la frecuencia natural del sistema para mejorar su ganancia.

polo resonante =

$$\frac{1}{(s^2 + \omega_0^2)}$$

(53)

Utilizando Sisotool, una herramienta de MATLAB para diseñar controladores, se ubica el polo resonante a la frecuencia natural de la red, 60 Hz o 377 rad/s. luego se colocan 3 ceros para compensar el efecto del polo resonante y además se agrega un integrador para eliminar el error en estado estable, luego manipulando la ganancia del sistema se debe asegurar que se obtenga el Margen de Fase deseado de 60° y que la frecuencia de corte sea de 600 Hz, para que el ancho de banda sea el indicado.

**Figura 18.** Diseño del controlador con polo resonante para la planta de voltaje de la Etapa DC-AC, utilizando la herramienta Sisotool de Matlab.

Por lo tanto la ganancia del controlador será:

$$G_c(s) = \frac{3330(s+9990)(s+188)^2}{s(s+4343)(s^2+(376.9911)^2)}$$

(54)

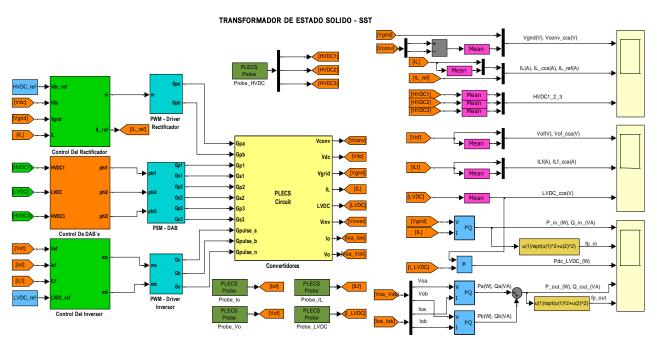

### 5 Implementación y Simulación del SST.

Una vez diseñado los componentes y controladores de cada bloque que conforman el SST, se realiza la implementación en SIMULINK. Con el objetivo de analizar y verificar la estabilidad y correcto funcionamiento del SST ante la presencia de perturbaciones que son características en los sistemas de potencia se realizarán las siguientes pruebas simulando dichas perturbaciones y se analizará el comportamiento del SST ante las mismas.

Figura 19. Diagrama del Transformador de Estado Sólido (SST) implementado en SIMULINK.

#### 5.1 Análisis de las Simulaciones del SST.

# 5.1.1 Simulación de un SAG y SWELL del 20% en el Voltaje de la Red.

Los SAG y SWELL son perturbaciones que se manifiestan como reducciones o incrementos no muy grandes y por poco tiempo en la forma de onda del voltaje.

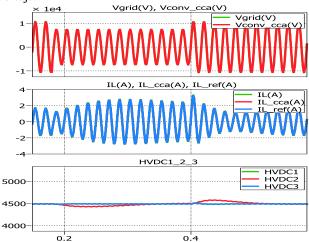

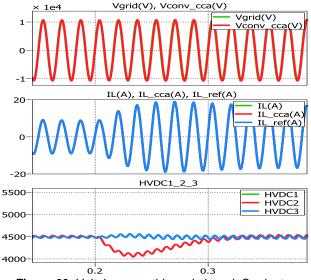

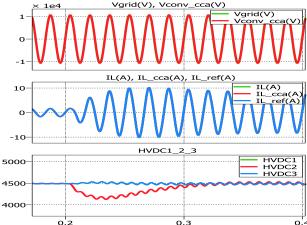

**Figura 20.** Voltaje convertidor y de la red, Corriente IL\_HVDC y Voltajes HVDC.

Se observa la caída de voltaje en la red por un instante de tiempo, el voltaje de la red se reduce al igual que el voltaje en el convertidor y para compensar la potencia que debe entregar el SST la corriente en el convertidor aumenta.

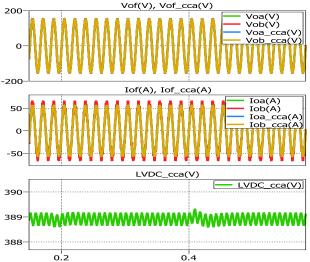

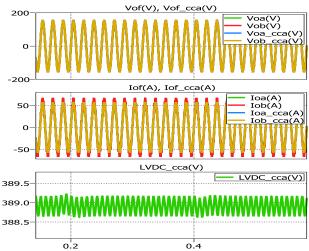

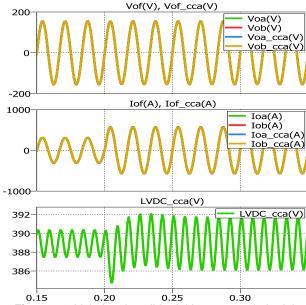

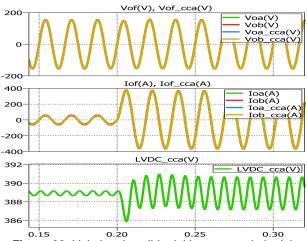

**Figura 21.** Voltajes de salida del inversor, voltaje del convertidor, corrientes de salida del inversor y voltaje LVDC.

Las formas de ondas de voltaje y corrientes a la salida del inversor no son afectadas porque los capacitores entregan parte de su potencia para mantener la potencia constante a la salida.

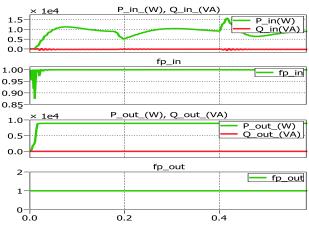

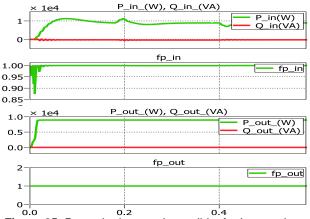

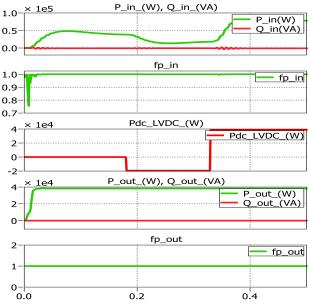

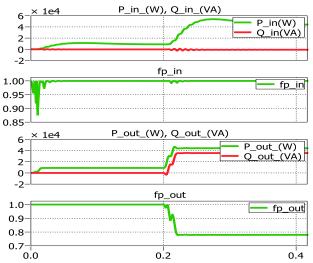

**Figura 22.** Potencia de entrada y salida, fp de entrada y salida.

Se observa que las potencias y el factor de potencia tanto a la entrada como a la salida del convertidor, la potencia de entrada se reduce durante el tiempo que dura el SAG pero la potencia de salida se mantiene constante gracias a la potencia entregada por los capacitores.

**Figura 23.** Voltaje convertidor y de la red, Corriente IL\_HVDC y Voltajes HVDC.

Se observa el aumento de voltaje en la red por un instante, el voltaje de la red se incrementa al igual que en el convertidor y para compensar la potencia que debe entregar el SST la corriente disminuye. Las formas de ondas de voltajes y corrientes del inversor no son afectadas por un SWELL del 20% en el voltaje de la red como se muestra a continuación.

**Figura 24.** Voltajes de salida del inversor, voltaje del convertidor, corrientes de salida del inversor y voltaje LVDC.

Las formas de ondas de voltaje y corrientes a la salida del inversor no son afectadas debido a que los capacitores entregan parte de su potencia para mantener la potencia constante a la salida. Las potencias y el factor de potencia tanto a la entrada como a la salida del convertidor, la potencia de entrada se incrementa durante el tiempo que dura el SWELL pero la potencia de salida se mantiene constante por la potencia entregada por los capacitores.

**Figura 25.** Potencia de entrada y salida, fp de entrada y salida.

# 5.1.2 Inyección de Potencia en el Enlace DC de Baja Tensión.

El SST permite integrarnos a redes inteligentes y utilizar fuentes de energía alternativa ya que se tiene el Enlace LVDC el cual permite alimentar a cargas DC o el acceso de fuentes de energía para proveer energía a la red. Simularemos una inyección de potencia DC y una extracción de potencia DC, la perturbación DC de 50(A) estará entre  $0.1 \le t_1 \le 0.2$  y para la perturbación DC de 100(A) estará de  $0.2 \le t_2$  en adelante.

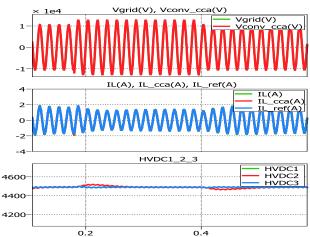

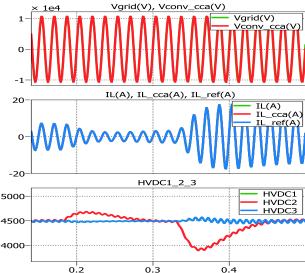

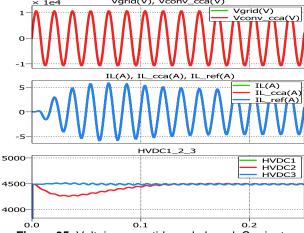

**Figura 26.** Voltaje convertidor y de la red, Corriente IL\_HVDC y Voltajes HVDC.

Al momento de simular el consumo de potencia DC el voltaje de la red y el convertidor muestran un pequeño aumento y por lo tanto la corriente IL\_HVDC disminuye para compensar la potencia que entrega el convertidor, por otro lado al momento de adición de potencia DC el voltaje de la red y del convertidor disminuyen un poco y la corriente IL\_HVDC es la encargada de aumentar su valor para compensar la potencia a la salida del convertidor. Los voltajes del enlace HVDC aumentan y disminuyen respectivamente para mantener los voltajes y corrientes a la salida del inversor permanezcan estables.

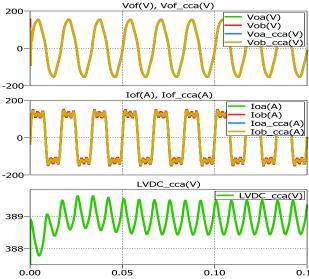

**Figura 27.** Voltajes de salida del inversor, voltaje del convertidor, corrientes de salida del inversor y voltaje LVDC.

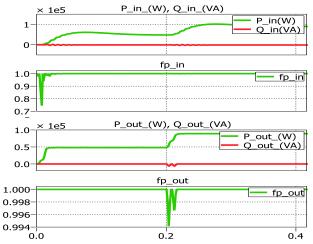

Se observa que la potencia de entrada disminuye al momento de consumir potencia DC y que aumenta al momento de inyectarse potencia DC, la potencia DC muestra su respectivo cambio de signo en la potencia al omento de inyectar y consumir potencia DC, la potencia de salida permanece constante debido a que sus valores de voltaje y salida no presentaron cambio alguno.

**Figura 28.** Voltajes de salida del inversor, voltaje del convertidor, corrientes de salida del inversor y voltaje LVDC.

# 5.1.3 Condición de Máxima Carga y Sobrecarga.

Como todo equipo eléctrico, el SST debe soportar sobrecargas en el sistema, para lo cual se agrega una sobrecarga, para comprobar el correcto funcionamiento del SST.

Figura 29. Voltaje convertidor y de la red, Corriente IL\_HVDC y Voltajes HVDC.

Al aumentar la carga aumenta la corriente de entrada y de salida, manteniéndose el voltaje de salida constante, tal como se observa. Estas variaciones de potencia se ven reflejadas en los voltajes DC que transmiten la potencia requerida por la carga, por lo que se puede apreciar en las gráficas que el nivel de voltaje disminuye y el control logra estabilizarlos obteniendo mayor potencia de la red, después de un instante de tiempo.

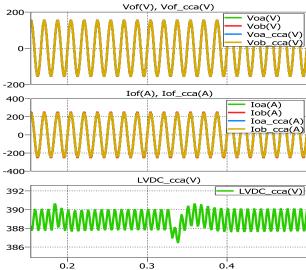

**Figura 30.** Voltajes de salida del inversor, voltaje del convertidor, corrientes de salida del inversor y voltaje LVDC.

La gráfica muestra el aumento de la potencia de entrada y de salida debido a la sobrecarga en el sistema y los factores de potencia se mantienen en 1 respectivamente debido a que se está trabajando con carga resistiva.

**Figura 31.** Voltajes de salida del inversor, voltaje del convertidor, corrientes de salida del inversor y voltaje LVDC.

### 5.1.4 Bajo de Factor de Potencia.

El SST debe ser capaz de funcionar bajo la presencia de una carga con bajo factor de potencia. Se colocara una carga con un fp = 0.7 lo cual es multado por la empresa proveedora de energía eléctrica. Las características de esta carga es R= 0.34 [ $\Omega$ ] y L= 0.9077 [mH] la misma que será conectada en un  $t \geq 0.2$ , además de esperar un correcto funcionamiento de las variables de voltaje y corriente dicho factor de potencia no debe afectar nuestro factor de potencia a la entrada.

**Figura 32.** Voltaje convertidor y de la red, Corriente IL\_HVDC y Voltajes HVDC.

Se observa como los voltajes se mantienen estables y la corriente de la carga aumenta debido a la carga reactiva que entra al sistema. Esto se debe a que los capacitores son los encargados de entregar la potencia reactiva necesaria a la carga sin afectar la potencia que entra al SST.

**Figura 33.** Voltajes de salida del inversor, voltaje del convertidor, corrientes de salida del inversor y voltaje LVDC.

La potencia activa de entrada del SST se aumenta a un 60% ya que la potencia activa en la carga aumento a un 60%, sin verse afectada la potencia reactiva, por lo tanto se tiene un factor de potencia unitario en la entrada del SST. La potencia reactiva en la carga hace que el factor de potencia de salida disminuya y sea aproximadamente 0.8 que está en un rango permisible por el SST y lo puede controlar.

**Figura 34.** Voltajes de salida del inversor, voltaje del convertidor, corrientes de salida del inversor y voltaje LVDC.

#### 5.1.5 Presencia de Armónicos.

Verificar el correcto funcionamiento del SST ante la presencia de armónicos es necesaria debido a que es bastante común en los sistemas de potencia, particularmente en corrientes.

Para la prueba se inyecta en el sistema una corriente armónica del lado de la carga, de la prueba observaremos el comportamiento de las variables de corriente y voltaje de entrada y de salida.

**Figura 35.** Voltaje convertidor y de la red, Corriente IL\_HVDC y Voltajes HVDC.

La corriente de carga presenta armónicas, que distorsionan la forma de onda sinusoidal, pero el voltaje de salida no presenta armónicas, debido a que la respuesta rápida del control no permite que el voltaje se distorsione.

**Figura 36.** Voltajes de salida del inversor, voltaje del convertidor, corrientes de salida del inversor y voltaje LVDC.

#### **Conclusiones:**

- Se cumplió con el dimensionamiento de inductancias y capacitancias para cada etapa del SST de 100 KVA.

- Se demuestra que el diseño de control en las diferentes etapas del SST se realizó con éxito, esto se observa en la respuesta de control en cada etapa del SST al aplicarle perturbaciones en las pruebas a las que fue sometido.

- Se observa que a través del enlace DC del SST, la potencia se distribuye automáticamente entre la carga del SST, confirmando un flujo de potencia multidireccional y dinámico.

#### **Recomendaciones:**

- Si se desea implementar este trabajo, se debe usar los valores de los componentes aquí calculados, ya que si los variamos demasiado el sistema puede volverse inestable.

- Si se desea trabajar a otra potencia y voltajes, se recomienda hacer los cálculos nuevamente, debido a que los componentes trabajan con los valores y rizados establecidos.

- Es recomendable tener en cuenta que el ancho de banda entre el controlador de corriente y voltaje debe estar separado por lo menos una década. Además se recomienda usar polo resonante si el ancho de banda del controlador de voltaje se acerca a la frecuencia natural, para incrementar su ganancia y obtener una mejor respuesta del controlador.

#### **Referencias:**

- [1] Falcones, S., Mao, X., y Ayyanar, R, "Simulation of the FREEDM Green Hub with Solid State Transformers and Distributed Control", 2013.

- [2] Rodríguez, F., & Fayos, A. (1998). "El transporte de la energía eléctrica en alta tensión". Valencia: Universidad Politécnica de Valencia, fecha de consulta Mayo 2013.

- [3] Endesa Red S.A. (2012). "Las Redes Inteligentes", fecha de consulta Mayo 2013.

- [4] "Solid state transformers ready to enable the smart grid" Michael J. Kawa FREEDM; http://www.freedm.ncsu.edu/index.php?s=2&t=n ews&p=121, Junio 2013.

- [5] Falcones, Mao; "Topology Comparison for Solid State Transformer Implementation"; Ayyanar. Arizona IEEE 2010.

- [6] Urrutia Fernando Valdés Francisco; "Estado del Arte Sobre Topologías de Convertidores Multinivel"; UBB.

- [7] Martínez Hernández; "Control digital para convertidor multinivel alimentado con energía solar"; Universidad de las Américas Puebla Escuela de Ingeniería y Ciencias.

- [8] Revelo Andrade; "Convertidores CD/CA multinivel"; Universidad de las Américas Puebla Escuela de Ingeniería y Ciencias.

- [9] Jacobi Diego, Pfarher Iván; "Control de Potencia Monofásica por SPWM - Aplicaciones en: Control de Potencia y la Industria"; Universidad Tecnológica Nacional Facultad Regional Paraná. Argentina - Entre Ríos -Paraná.

- [10] Hamid R. Karshenas 1,2, Hamid Daneshpajooh 2, Alireza Safaee 2; 1"Bidirectional DC-DC Converters for Energy Storage Systems"; Department of Elec. & Computer Eng., Queen's University, Kingston; 2Isfahan University of Tech., Isfahan.

- [11] Zong X., A Single Phase Grid Connected DC/AC Inverter with Reactive Power Control for Residential PV Application .2011

- [12] Ayyanar, R., K-Factor approach, EEE 572 Arizona State University, 2009.