# ESCUELA SUPERIOR POLITECNICA DEL LITORAL

Facultad de Ingeniería en Electricidad y Computación

# REINGENIERIA DE LA UNIDAD DE CARGADO DEL PROGRAMA OPERATIVO DEL SISTEMA DE GUERRA ELECTRÓNICA NS-9010-EC DE LAS UNIDADES CLASE "QUITO"

**TESIS DE GRADO**

Previa la obtención del Título de:

INGENIERO EN ELECTRICIDAD

ESPECIALIZACION ELECTRONICA

Presentada por:

Boris Eduardo Brito Moreno

GUAYAQUIL-ECUADOR

ANO

2001

#### **AGRADECIMIENTO**

A la Armada del Ecuador, por promover mi capacitación profesional, de manera especial al Centro de Investigación y Desarrollo Naval.

A la Ing. Helen Vega, Directora de Tesis, por su invaluable y desinteresado apoyo.

Al Ing. Rodrigo Moscoso, por su paciencia y sus consejos.

# **DEDICATORIA**

A DIOS,

A MARIA ANGELINA,

A MI MADRE.

A MI HERMANA Y MIS SOBRINOS.

#### **DECLARACION EXPRESA**

"La responsabilidad del contenido de esta Tesis de Grado, me corresponden exclusivamente; y el patrimonio intelectual de la misma a la ESCUELA SUPERIOR POLITECNICA DEL LITORAL".

(Reglamento de Graduación de la ESPOL).

Boris Eduardo Brito Moreno

# TRIBUNAL DE GRADUACION

Ing. Carlos Monsalve

Parla March

SUB-DECANO DE LA FIEC

Ing. Helen Vega

DIRECTORA DE TESIS

Ing. Norman Chootong

MIEMBRO

Ing. Sara Rios

**MIEMBRO**

# INDICE GENERAL

| RESUMEN                                | VI   |

|----------------------------------------|------|

| INDICE GENERAL                         | VII  |

| ABREVIATURAS                           | XII  |

| INDICE DE FIGURAS                      | XIII |

| INDICE DE TABLAS                       | xv   |

| INDICE DE ANEXOS                       | XVI  |

| INTRODUCCION                           | 1    |

| 1 EL SISTEMA NS-9010-EC                | 2    |

| 1.1 Descripcion del equipo             | 2    |

| 1.1.1 Especificaciones generales       | 2    |

| 1.1.2 Descripción física               | 4    |

| 1.1.3 Descripción funcional            | 6    |

| 1.1.4 Operación                        | 9    |

| 1.2 El Grupo de Procesamiento y el MRU | 10   |

| 1.2.1 CPU                              | 12   |

| 1.2.2 Interfases de entrada y salida   | 14   |

| 1.2.3 Memoria de 128 K                 | 15   |

|   | 1.2.4 Disquetera de 8 pulgadas: MRU                           | 23  |

|---|---------------------------------------------------------------|-----|

|   | 1.3 Dispositivos de almacenamiento de memoria                 | 32  |

|   | 1.3.1 Las unidades de disco flexible                          | 32  |

|   | 1.3.2 Las unidades de disco flexible de 120 MB                | 39  |

|   | 1.3.3 Memorias SRAM                                           | 41  |

|   | 1.3.4 Memorias EPROM                                          | 42  |

|   | 1.3.5 Memorias NVSRAM                                         | 42  |

| 2 | ANÁLISIS DEL PROBLEMA                                         | 45  |

|   | 2.1 Situación actual del equipo                               | 45  |

|   | 2.1.1 Proceso de almacenamiento del Programa Operativo        | 45  |

|   | 2.1.2 Ciclo de escritura y lectura                            | 46  |

|   | 2.1.3 Diagrama eléctrico de alimentación de las memorias      | 48  |

|   | 2.2 Planteamiento del problema                                | 51  |

|   | 2.2.1 Capacidad operativa de la unidad                        | 54  |

|   | 2.2.2 Operatividad del equipo                                 | 54  |

| 3 | ALTERNATIVAS DE POSIBLES SOLUCIONES                           | 55  |

|   | 3.1 Recuperacion de la cap. operativa de la lae Quito         | 55  |

|   | 3.2 Recuperacion de la operatividad del NS9010-EC             | _56 |

|   | 3.3 Diseño del nuevo dispositivo de almacenamiento de memoria | 60  |

|   | 3.4 Solución planteada                                        | 62  |

| DISEÑO I  | DEL PROTOTIPO RESPALDO DE BATERÍA                        | 63  |

|-----------|----------------------------------------------------------|-----|

| 4.1 Bater | ia recargable                                            | 63  |

| 4.1.1     | Proceso de descarga                                      | 64  |

| 4.1.2     | Proceso de carga                                         | 66  |

| 4.1.3     | Tensión de reposo                                        | 67  |

| 4.1.4     | Tensión nominal                                          | 67  |

| 4.1.5     | Tensión de descarga                                      | 67  |

| 4.1.6     | Tensión final de descarga y tension final en funcion del |     |

|           | sistema                                                  | 69  |

| 4.2 Espe  | cificaciones generales del diseño                        | 70  |

| 4.3 Dime  | nsionamiento de la batería                               | 71  |

| 4.3.1     | Capacidad                                                | 71  |

| 4.3.2     | Rendimiento y factor de carga                            | 72  |

| 4.3.3     | Análisis de parámetros del banco de memorias             | _72 |

| 4.3.4     | Análisis de recarga de la batería                        | 73  |

| 4.4 Desa  | arrollo del prototipo                                    | 75  |

| 4.4.1     | Implantación                                             | 75  |

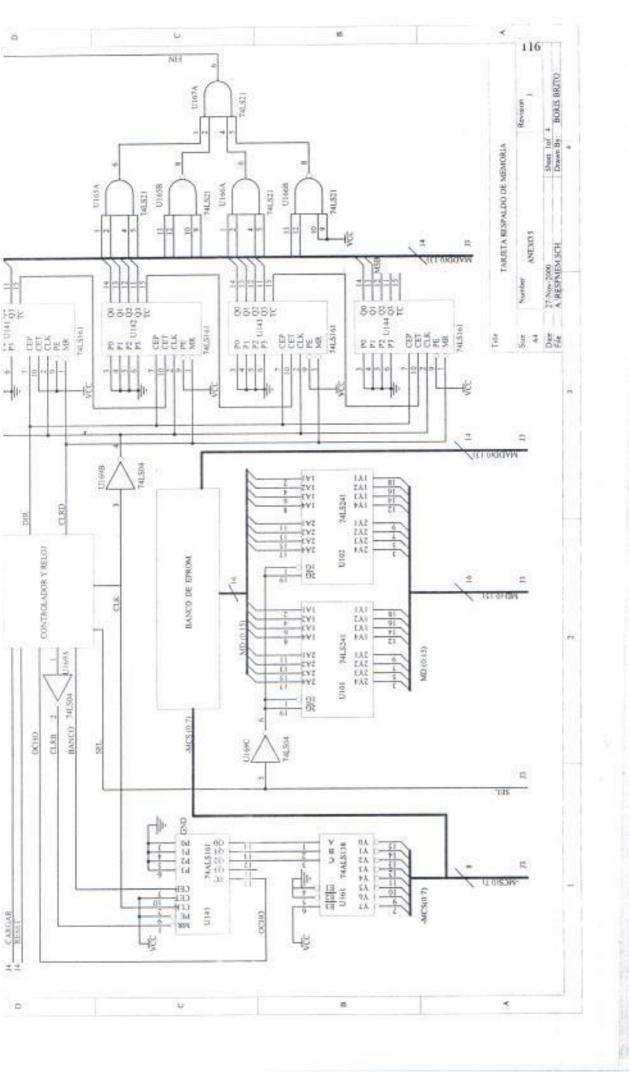

| 4.4.2     | Circuito respaldo de Batería diagrama eléctrico          | 77  |

| 4.4.3     | Instalación                                              | 77  |

| 4.4.4     | Operación del circuito                                   | 78  |

| 445       | Localización                                             | 79  |

|      |        | 4.4.6 | Lista de componentes                             | 79   |

|------|--------|-------|--------------------------------------------------|------|

|      | 4.5    | Sele  | cción de la bateria                              | 80   |

| 5    | DES    | ARR   | OLLO DEL PROTOTIPO RESPALDO DE MEMORIA           | 81   |

|      | 5.1 [  | Espe  | cificaciones generales del diseño                | 81   |

|      | 5.2 [  | Disei | ño del prototipo                                 | 82   |

|      | 5      | 5.2.1 | Elección de las NVSRAM para el banco de memorias | 84   |

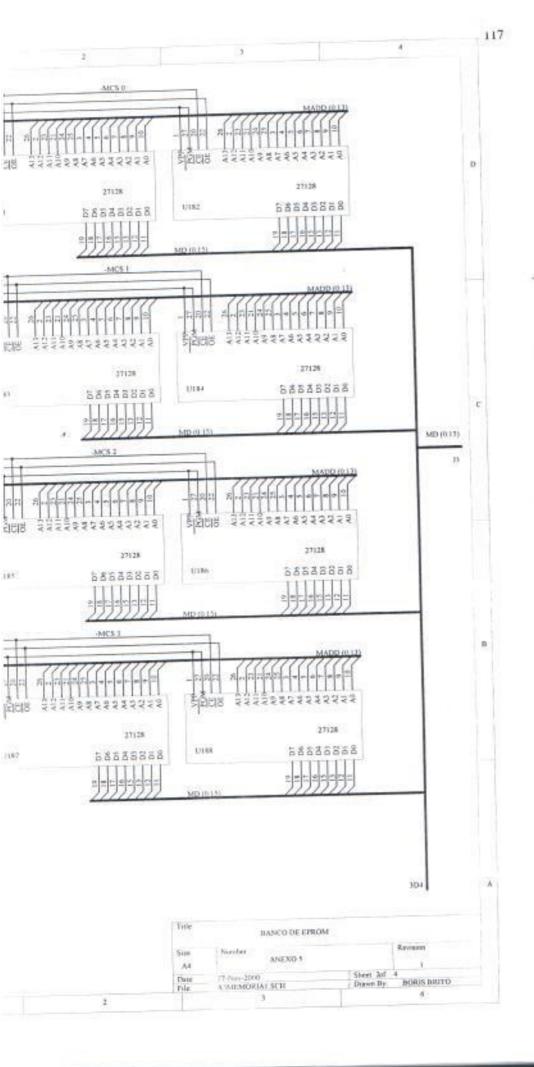

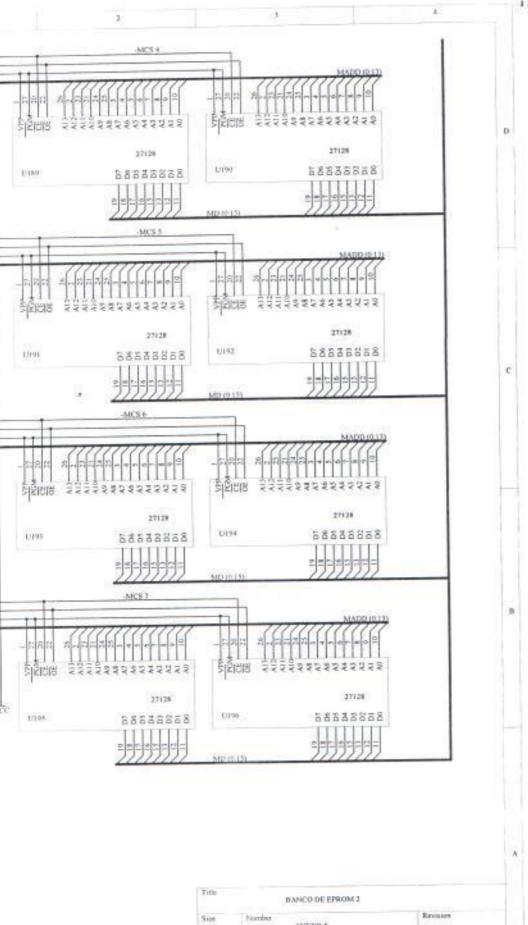

|      | 5      | .2.2  | Elección de las EPROM                            | 89   |

|      | 5      | .2.3  | Diagrama del prototipo                           | _ 90 |

|      | 5      | .2.4  | Implantación                                     | 93   |

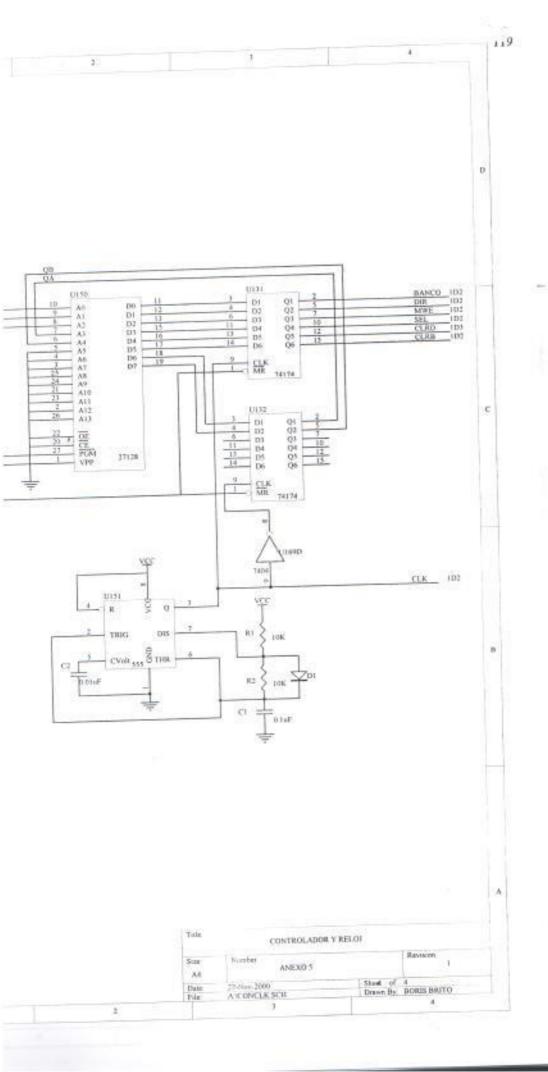

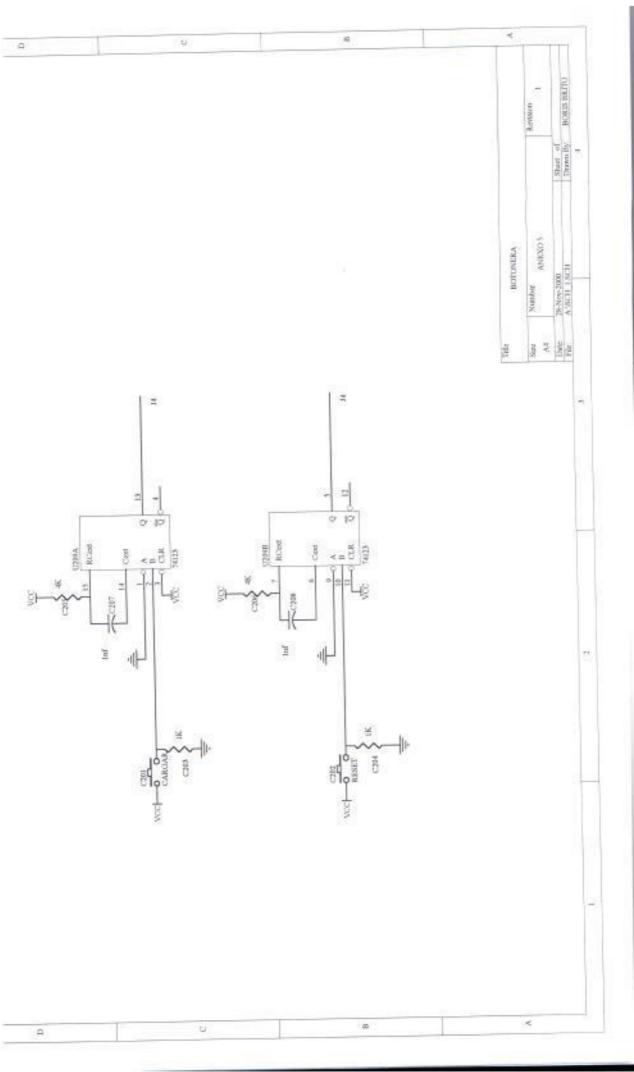

|      |        |       | Diseño del controlador                           |      |

|      | 5      | .2.6  | Señales del conector J3/P3                       | 100  |

|      | 5      | .2.7  | Lista de componentes                             | 101  |

|      | 5.3 (  | per   | ación                                            | 102  |

|      | 5.4 F  | unci  | ionamiento                                       | 103  |

| VI   | CONC   | LUS   | IONES                                            | 105  |

| VII  | RECO   | MEN   | NDACIONES                                        | 108  |

| VIII | ANEX   | cos   |                                                  | _109 |

| IX E | BIBLIC | )GR   | AFIA                                             | 121  |

#### **ABREVIATURAS**

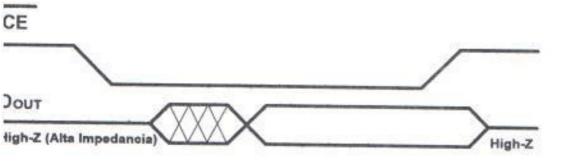

CE Deshabilitación del integrado (Chip Enable).

CS Selección del Integrado (Chip Select).

EPROM Memoria PROM borrable (Erasable PROM).

ESCLAM Escuadrón de Lanchas Misileras.

FEM Fuerza Electromotriz

GIROCOMPAS Dispositivo de orientación de la unidad respecto al Norte

Verdadero

IBM International Business Machine

LAE Lancha de la Armada del Ecuador.

MRU Unidad de Grabado Magnético (Magnetic Recording Unit).

NVSRAM Memoria RAM no volátil (No Volatil Static RAM).

PAL Arreglo Lógico Programable (Programmable Array Logic).

PC Computador Personal (Personal Computer)

R Lectura (Read)

SRAM Memoria RAM estática (Static RAM).

W Escritura (Write).

# INDICE DE FIGURAS

| Fig. 1.1 | Diagrama de Bloques del NS-9010-EC.                     | 6  |

|----------|---------------------------------------------------------|----|

| Fig. 1.2 | Diagrama de Bloques del Grupo de Procesamiento.         | 11 |

| Fig. 1.3 | Diagrama de Bloques del CPU.                            | 13 |

| Fig. 1.4 | Diagrama de Bloques de la memoria de 128 K.             | 17 |

| Fig. 1.5 | Diagrama de tiempo de Lectura/ Escritura de la Memoria. | 22 |

| Fig. 1.6 | Sistema de disquette-interfase.                         | 24 |

| Fig. 1.7 | Diagrama de Bloques del MRU.                            | 28 |

| Fig. 1.8 | Diagrama de Tiempo de Escritura y Lectura de Datos del  | 30 |

|          | MRU.                                                    |    |

| Fig.1.9  | Diagrama de bloques de una disquetera de 3.5            | 37 |

|          | pulgadas.                                               |    |

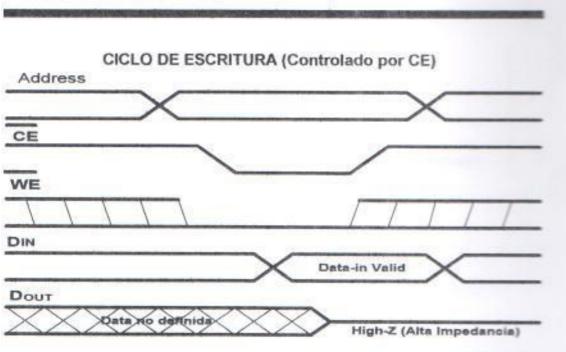

| Fig. 2.1 | Ciclo de Escritura y Lectura de las memorias SRAM.      | 47 |

| Fig. 2.2 | Diagrama de bloques de la alimentación eléctrica de las | 49 |

|          | memorias.                                               |    |

| Fig. 2.3 | Configuración Eléctrica maestro-esclavo del banco de    | 51 |

|          | memorias SRAM.                                          |    |

| Fig. 4.1 | Diagrama de bloques de la implantación del prototipo    | 75 |

| Fig. 5.1 | Diagrama de Bloques del Prototipo.                      | 85 |

| Fig. 5.2 | Unidades de Memoria del NS-9010 V1.                     | 88 |

| Fig. 5.3 | Diagrama del Prototipo.                                 | 92 |

| Fig. 5.4 | División del Prototipo por bloques                 | 94 |

|----------|----------------------------------------------------|----|

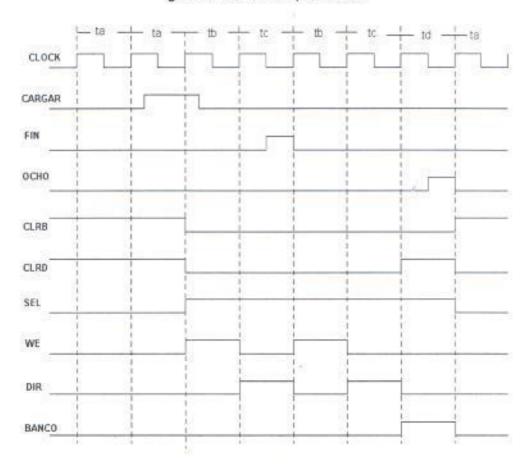

| Fig. 5.5 | Diagrama de Tiempo de las señales del Controlador. | 98 |

# INDICE DE TABLAS

| Tabla I    | Distribución de Pines de la disquetera de 3.5".           | 40  |

|------------|-----------------------------------------------------------|-----|

| Tabla II   | Lectura y Escritura de las memorias SRAM.                 | 46  |

| Tabla III  | Tabla causa- efecto- consecuencias.                       | 53  |

| Tabla IV   | Características funcionales de las memorias NVSRAM.       | 86  |

| Tabla V    | Modo de Operación de las SRAM.                            | 86  |

| Tabla VI   | Modo de Operación de las NVSRAM.                          | 87  |

| Tabla VII  | Cuadro de equivalencias de las señales de control de las  | 89  |

|            | SRAM y NVSRAM.                                            |     |

| Tabla VIII | Características funcionales de las memorias EPROM         | 91  |

|            | 27128.                                                    |     |

| Tabla IX   | Equivalencia de pines para la lectura (EPROM) y escritura | 91  |

|            | (NVSRAM) de datos.                                        |     |

| Tahla X    | Señales del conector P3/13                                | 404 |

#### INTRODUCCION

- Las Lanchas Misileras clase QUITO están equipadas desde 1992, con un sistema de Guerra Electrónica NS-9010-EC de fabricación israeli, estos sistemas disponen de una unidad de cargado del programa operativo (MRU) que emplea una disquetera de 8" fabricada por la compañía MILTOPE, actualmente en obsolescencia.

- La ausencia de la unidad de cargado (MRU) de la Lancha Misilera "QUITO" ha conducido a que la operación de este sistema se vea restringida al apoyo que le pueda brindar cualquiera de las otras dos lanchas para cargar dicho programa, sin el cual no puede arrancar.

# CAPÍTULO 1

#### 1 EL SISTEMA NS-9010-EC

#### 1.1 Descripción del equipo

#### 1.1.1 Especificaciones generales

El NS-9010-EC ESM es un sistema avanzado de Guerra Electrónica, instalado en las Lanchas Misileras clase "QUITO", capaz de realizar las siguientes operaciones funcionales:

- Recepción, análisis e identificación de señales de radar en el rango de frecuencia de 1 a 18 GHz.

- Medición de la dirección de origen de las señales de radar con alta precisión.

- Cobertura simultánea de 360 grados con antenas omnidireccionales, espirales y antenas lente.

- Detección de la dirección de la emisión por el uso de la antena estática DF(direction finding), con 360 grados de azimuth y 20 grados de elevación.

- Presentación visual en una pantalla de 17" en los modos:

- Cartesiano: Frecuencia vs. Azimuth.

- Polar.

- Parámetros alfanuméricos para la identificación de emisiones recibidas.

- Alerta acústica para emisiones pre-programadas.

- Panel de control para la comunicación interactiva entre el operador y el sistema, usando:

- > Teclado de 4x4 para uso general.

- > Botones pulsantes para funciones especiales.

- Palanca (Joystick) para la designación de las emisiones detectadas.

- Computadora digital con:

- Palabras de 16 bits.

- Memoria de 128k word.

- Dos canales de Acceso Directo a Memoria DMA.

- Tiempo típico de ejecución de instrucciones:

1us.

- Identificación de las emisiones: Comparación de las emisiones detectadas con una librería preprogramada.

- Más de 100 emisiones programadas con las características:

- a) Parámetros de emisión.

- b) Nombre de la emisión.

- c) Prioridad de la emisión.

- d) Plataforma de la emisión.

- Dispositivos de interfase con el buque:

- a) Protección de los radares de la unidad.

- b) Con el girocompás del buque para

Marcación verdadera.

# 1.1.2 Descripción Física

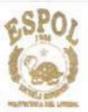

El sistema NS-9010-EC consta de los siguientes equipos, se presenta un diagrama de bloques en la fig. 1.1;

- a) CONSOLA DEL OPERADOR: ubicada en el CIC (Centro de Información de Combate), tiene las siguientes partes:

- PDU (Unidad de distribución de poder).

- LPU (Unidad de impresión en línea).

- ADU (Unidad de display de actividades).

- . CTU (Unidad de control de mesa).

- Panel de Audio.

- MRU (Unidad de grabado magnético).

- b) GAVETA DE EQUIPOS: También se encuentra en el CIC, se compone de:

- · RFU (Unidad de radiofrecuencia).

- IDU (IFM<sup>1</sup> digitizing unit).

- SPU (Unidad de procesamiento de señales).

- · CIU (Unidad central de interfase).

- PSU (Unidad de suministro de poder).

- c) IAU (Unidad de búsqueda de dirección intermedia y antena omnidireccional): Ubicada en la parte superior del mástil.

- d) FDA (Antena de detección de búsqueda de dirección fina): Consta de cuatro unidades similares ubicadas a los costados del mástil.

<sup>&</sup>lt;sup>1</sup> Medición de frecuencia intermedia

e) DPU (Unidad de procesamiento de búsqueda de dirección): Se ubica al pie del mástil.

Fig. 1.1 Diagrama de Bloques del NS-9010-EC

#### 1.1.3 Descripción Funcional

Con el fin de cubrir de manera eficiente sus parámetros de funcionamiento, el sistema cuenta con seis grupos funcionales bien definidos:

#### a) GRUPO RECEPTOR

Consta de una antena ominidireccional localizada en el IAU, la misma que recibe las señales de radiofrecuencia (RF), las señales recibidas son ruteadas al DPU, para posteriormente enviarlas al RFU e IDU localizados en la gaveta de equipos.

Estas unidades convierten las señales de radiofrecuencia en información digital de frecuencia, amplitud y ancho de pulso, para luego rutearlas hacía el grupo de procesamiento localizado en la gaveta de equipos.

# b) GRUPO DE RASTREO DE DIRECCION (DIRECTION FINDING GROUP):

Cuenta con seis antenas espirales localizadas en el IAU, y cuatro equipos FDA, cada uno cubriendo una zona de 90 grados. Las señales de radiofrecuencia son recibidas por estas antenas y luego ruteadas al DPU; las señales de amplitud de radiofrecuencia son convertidas en el DPU en palabras digitales, esta información digital se la rutea al grupo de

procesamiento, localizado también en la gaveta de equipos.

#### c) GRUPO DE PROCESAMIENTO:

Realiza el procesamiento, análisis e identificación de las señales de radar, también controla y monitorea todas las funciones de la consola del operador.

#### d) GRUPO DE CONTROL Y PRESENTACION:

Localizado en la consola del operador, proporciona información visual y auditiva al operador, y permite un completo control sobre todo el sistema. Se compone de los bloques LPU, ADU, CTU y MRU.

#### e) GRUPO DE SUMINISTRO DE PODER:

Cuenta con el PDU, localizado en la consola del operador y el PSU que se encuentra en la gaveta de equipos, este grupo distribuye el voltaje AC y provee el poder DC requerido para la operación del equipo.

#### f) GRUPO DE SOFTWARE

Está compuesto por rutinas de software que sirven para la operación del equipo, permite correr programas de diagnóstico, control y además carga el sistema operativo al equipo.

#### 1.1.4 Operación

El sistema es operado por un solo hombre, ubicado frente a la consola del operador. Generalmente se realizan las siguientes tareas para inicializar el equipo:

- a. El operador verificará que todos los interruptores en todas las unidades del sistema se encuentren en la posición ON.

- Se realizará la verificación de que todos los disyuntores (breakers) de los circuitos se encuentren en la posición de encendido.

- c. Verificar que el MRU<sup>2</sup> (Unidad de Grabado Magnético) se encuentre encendido y el disquete de carga del sistema operativo esté presente.

- d. Presionar el botón PRGM LOAD para cargar el sistema operativo desde el disquete al computador. La esquina marcada en ON deberá encenderse en un color verde para indicar que la carga del programa ha sido completada satisfactoriamente.

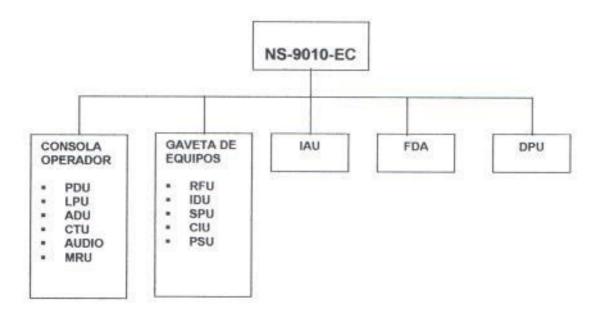

# 1.2 El Grupo de Procesamiento y el MRU

Contiene tres bloques principales, como indica la figura 1.2:

- · CPU.

- Interfases de Entrada y Salida.

- Banco de memoria de 128 k.

<sup>1</sup> Magnetic Recorder Unit

Fig. 1.2 Diagrama de Bloques del Grupo de Procesamiento

Estos bloques están compuestos de los siguientes sub-bloques:

- I/O interfase A.

- I/O interfase B.

- Controlador del canal de datos (DMA-1).

- Controlador del canal de datos (DMA-2).

- · Interfase del Control del Proceso (CPI).

- Interfase de la disquetera (FDI).

- · CPU.

#### Memoria de 128 K.

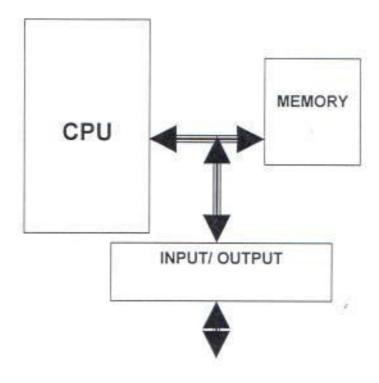

#### 1.2.1 CPU

El CPU es un procesador que ejecuta microprogramas de 52 bits en un ciclo de tiempo de 150-250 ns.

La operación de procesador es controlada por un programa operacional de software que se carga desde la disquetera de 8 pulgadas al banco de memorias de 128 k.

Cada instrucción del programa llama al procesador a realizar una acción específica, estas instrucciones pueden mover datos desde o hacia la memoria, desde o hacia los dispositivos de entrada y salida, realiza manipulaciones aritméticas y lógicas, controla la condición (status) de dispositivos externos.

En la figura 1.3 se observan las interrelaciones entre el procesador y los demás dispositivos; los operandos de las operaciones aritméticas y lógicas pueden ser localizadas en los acumuladores, o en algunos casos en la memoria. Las instrucciones aritméticas incluyen suma, resta,

complemento, inverso, multiplicación y división; las instrucciones lógicas incluyen OR, AND, OR exclusiva.

Fig. 1.3 Diagrama de Bloques del CPU.

Las especificaciones básicas del CPU son:

a. Organización de palabras de 16 bits.

- b. Controlado por microprogramas.

- Basado en la familia AMD 2900<sup>3</sup>.

- d. Cuatro acumuladores de 16 bits.

- e. Tiempo de ciclo de instrucciones de 150-250 nseg.

- Tiempo de ciclo de instrucciones aritméticas de 750 nseg.

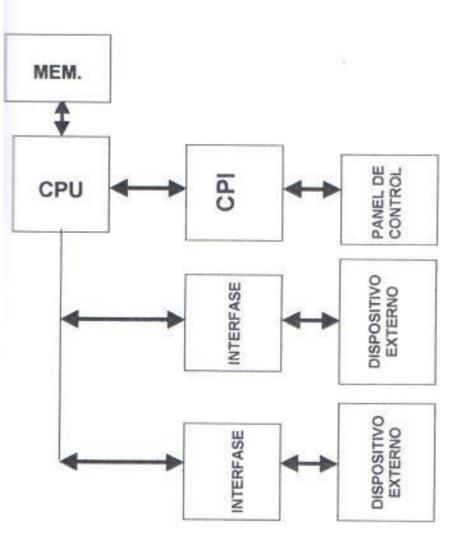

#### 1.2.2 Interfases de Entrada y Salida

Para que el CPU pueda actuar e interrelacionarse con los otros dispositivos, necesita un camino efectivo de transferencia de datos y control de señales, desde y hacia una variedad de sistemas externos.

El CPU se comunica con esos dispositivos a través del bus de entrada/ salida, el procesador realiza tres tipos de operaciones de entrada/ salida:

a. Las entradas y salidas programadas permiten al programa del procesador el control y transferencia de datos, desde o hacia la interfase de los dispositivos, para controlar y censar su condición.

<sup>&</sup>lt;sup>3</sup> Familia de microprocesadores de tecnología bit slice, muy usados en la década de los 80.

- El programa puede interrumpir las operaciones permitiendo que un determinado dispositivo se someta a una instrucción del procesador.

- c. El canal de acceso directo a memoria permite la transferencia de datos desde o hacia la memoria sin requerir la acción de una instrucción del programa.

Las siguientes son las especificaciones básicas de los interfases de entrada y salida:

- a. Bus de datos de 16 bits.

- b. Dispositivos direccionables de 64 x 3 bits.

- c. Prioridad de interrupción del DMA.

- d.Canal de acceso directo a memoria de 714 Kw/s4.

#### 1.2.3 Memoria de 128 K

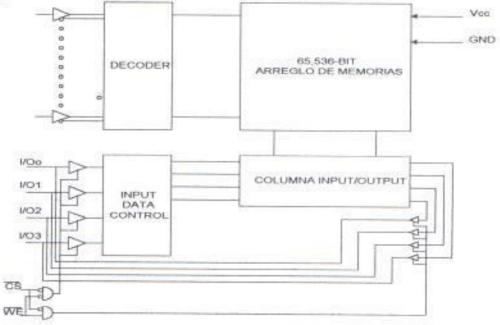

El banco de memoria es básicamente un dispositivo compuesto por memorias SRAM IDI 7188L70CBX (Anexo

1) manufacturadas de acuerdo a la tecnología CMOS,

<sup>4</sup> Kilopalabra por segundo

configuradas de modo que se almacene un máximo de 128k, organizados en palabras de 16 bits.

El CPU usa dos buses de direccionamiento de memoria:

- a. AWD: bus de 16 bits de datos y direcciones.

- b. RD: bus de 16 bits de lectura de datos.

De acuerdo con el método de banco de memorias, el dispositivo se ha dividido en grupos de 32 k, cada grupo es llamado BANCO. El banco cero (0) se denomina banco bajo y todos los demás son los bancos altos. En relación a las direcciones del CPU, el banco 0 serán las primeras 32k direcciones (000000 a 077777) octal, y todos los bancos superiores están en las siguientes direcciones (177777 a 100000) octal, especialmente las últimas 32k direcciones, es decir, desde el punto de vista del CPU todos los bancos superiores estarán en el mismo espacio de dirección.

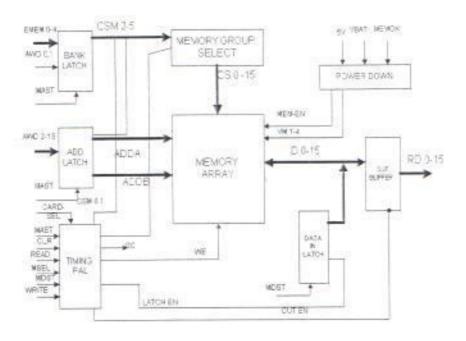

Un diagrama de bloques de la tarjeta de memoria se presenta en la figura 1.4, describiremos más adelante cada uno de los bloques:

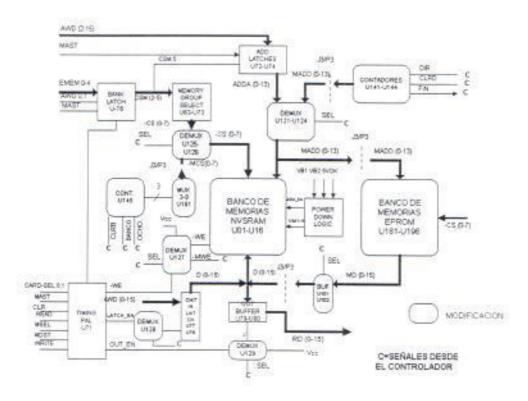

Fig. 1.4 Diagrama de Bloques de la memoria de 128 K.

- a. MEMORY ARRAY (ARREGLO DE MEMORIAS): Es el principal elemento de la unidad de memorias, su función es almacenar todos los programas del CPU (Programa Operativo), el arreglo de memorias contiene 32 SRAM de 16x4, organizados en grupos de 4 componentes, por lo cual existirán 8 unidades de memoria de 16k con palabras de 16 bits.

- b. ADD. LATCH: Almacena los datos de acuerdo a la dirección seleccionada por el CPU las direcciones

vienen conjuntamente con los datos en el bus AWD; para prevenir la sobrecarga, el bus de direcciones se multiplexa en dos idénticos buses: ADD A y ADD B, el NS-9010EC únicamente utiliza el bus ADD A...

- c. BANK LATCH: Es un suplemento del ADDRESS LATCH y también almacena los datos de acuerdo al número de bloque de memoria seleccionado.

- d. MEMORY GROUP SELECT: Cuatro bits, CM2-CM5, son usados para seleccionar una de las 8 unidades de memoria, las direcciones del grupo de memoria se reciben desde el Address Latch. El grupo de memoria es seleccionado cuando la señal CS5 es recibida desde el PAL<sup>6</sup>

- e. DATA IN LATCH: Almacena los datos requeridos por el CPU para ser escritos a la dirección previamente seleccionada a través del address latch, estos datos son recibidos por medio del bus AWD cuando la señal MDST

Programmable Array Logic: Arregio lógico que implementa la función de transferencia de la

lógica Booleana (suma de productos), por un integrado programable.

<sup>5</sup> Chip Select

(Memory Data Strobe) se activa. Los datos son enviados desde el arreglo de memoria cuando las señales de tiempo apropiadas son recibidas desde el PAL.

- f. OUT BUFFER: Funciona como buffer y como driver del bus de datos de salida desde la memoria; el contenido de la memoria se envía en el bus RD al CPU.

- g. TIMING PAL: Este bloque funciona como un controlador de tiempo para la memoria y contiene un 18P8B PAL. Las salidas de la señal de tiempo desde el PAL dependen de las señales de tiempo provenientes desde el CPU.

- h. POWER DOWN LOGIC: Provee alimentación continua a las memorias, permite que las unidades de memoria almacenen el Programa Operativo todo el tiempo, aún cuando la fuente de poder sea desconectada.

1.2.3.1 Teoria de Operación de la Memoria de 128 k:

Tiene dos modos de operación: lectura y escritura.

a. MODO DE LECTURA: El ciclo de lectura comienza con el arribo de las direcciones de memoria solicitadas desde el CPU. Las direcciones (AWD0 a AWD15) son muestreadas por el bloque ADDRESS LATCH y al mismo tiempo se selecciona el banco de memoria requerido a través de la señal MAST. Las dos señales MSB ( Most Significant Bit) del BANK LATCH (CSM0 y CSM1) seleccionan la salida de la señal CS al CPU. A continuación de la señal MAST (Memory Address Strobe), el CPU envia un pulso CLR el cual acciona en el PAL una señal de salida CS, el mismo que permite, en conjunto con los cuatro CSM, la selección de uno de los 8 grupos de memoria. Después de un periodo de estabilidad durante el cual la memoria seleccionada es leida, se envian

los datos (D0 a D15) por el bus RD a través del BUFFER de salida el cual se encuentra habilitado.

b. MODO DE ESCRITURA: La escritura de las memorias comienza exactamente igual que el ciclo de lectura; una dirección es enviada a través del bus AWD y el banco apropiado es seleccionado, las señales involucradas son mostradas por la señal MAST, entonces el CPU envia los datos a ser escritos sobre el bus de AWD: Estos datos son mostrados por el bloque DATA IN LATCH solamente con la señal MDST. El PAL, a su vez, envía una señal CS, la cual causa la selección del grupo de memoria donde se realizará la escritura. Al mismo tiempo la salida de las memorias se apaga por medio de la señal WE, el CPU envía un comando de escritura y al mismo tiempo los datos son

escritos en la dirección seleccionada de la unidad de memoria. En el diagrama de tiempo de lectura/escritura de las memorias (fig. 1.5), se puede apreciar la habilitación de las señales, en cada uno de los modos.

Fig. 1.5 Diagrama de tiempo de Lectura/ Escritura de la Memoria

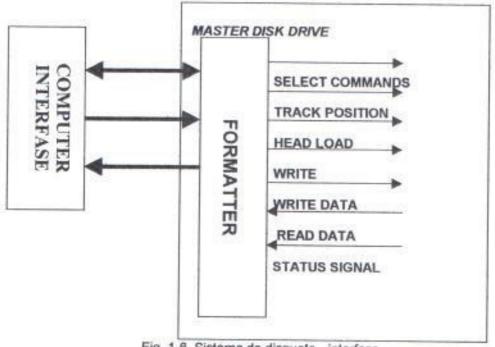

#### 1.2.4 Disquetera de 8 pulgadas: MRU

La disquetera de 8 pulgadas, denominada en el equipo como MRU (Magnetic Recorder Unit) es la unidad encargada de realizar las operaciones del grupo de software, es decir, este dispositivo lee la información del disquete de 8 pulgadas que contiene el sistema operativo y lo transfiere al banco de memorias del NS-9010-EC.

#### 1.2.4.1 Características Generales:

La unidad de disquete de 8 pulgadas es capaz de proveer mas de 6.4 millones de bits al realizar la lectura de los disquetes flexibles de 8 pulgadas. Cada disquete flexible contiene 77 tracks (pistas) concéntricos los cuales guardan alrededor de 83.000 bits de datos; cualquier localización de las direcciones y datos guardados en el disco puede ser accesada y transferida en alrededor de 500.000 bits por segundo.

El tiempo de acceso es de 6 milisegundos por track (pista), más 10 milisegundos para la

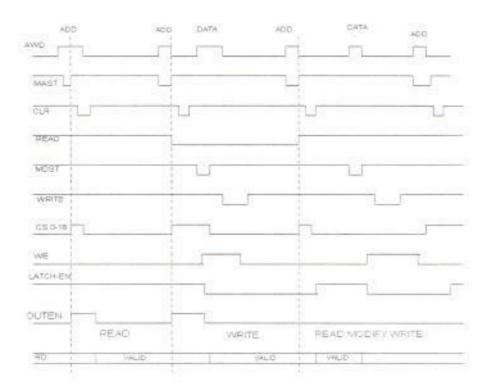

estabilización de la cabeza lectora. Está equipado con una tarjeta denominada FORMATTER, la misma que controla multiplexa el flujo de datos hacia la computadora, para que los datos recibidos por esta última estén en paralelo, además hace las veces de puerto de entrada del equipo y la disquetera. Esta tarjeta acepta señales de control, comando y datos desde el computador y permite el control del funcionamiento de la disquetera (ver fig. 1.6).

Fig. 1-6 Sistema de disquete - interfase

## 1.2.4.2 Diagrama de Bloques:

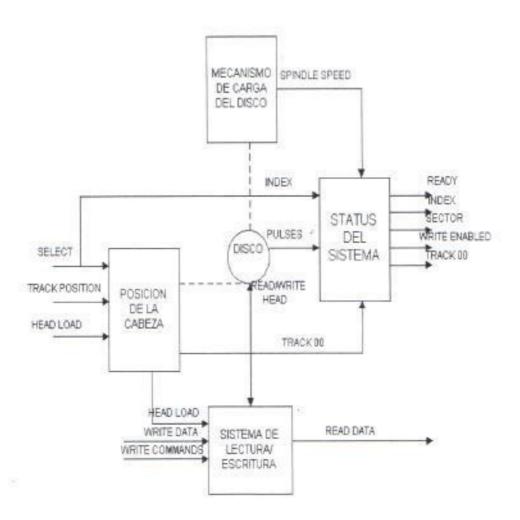

El diskdrive está dividido en los bloques (ver fig. 1-7):

### MECANISMO DE CARGA DEL DISCO.

Proporciona las señales de carga y descarga del disco flexible en la disquetera y de control de la velocidad de rotación del disquete cargado a 360 RPM. El sistema de la disquetera (drive) consta de un motor de corriente continua directamente acoplado a un circuito que controla el motor. Cuando la disquetera se prende, el circuito aplica 5 voltios DC al motor provocando que rote a 360 RPM; el disco flexible es enganchado por un cono que lo sostiene y lo fija para su rotación preestablecida.

### STATUS DEL SISTEMA

Controla continuamente a la disquetera y al disquete de modo que estén operando bajo el control de las señales que entrega y recibe el bloque FORMATTER. Cuando no existe un

disquete cargado, un fototransductor sensa la falta del mismo; cuando existe el disquete presente, el mismo fototransductor genera un pulso de índice por revolución; estos pulsos son usados para indicar que el disco está rotando en la disquetera.

Una señal importante es la habilitación de escritura, puesto que muestra al operador que el disquete se encuentra listo para ser grabado.

## POSICIONAMIENTO DE LA CABEZA Y CARGA DEL SISTEMA

Responden a comandos de posición desde el controlador para mover la cabeza del lectoescritura por cada pulso de paso, mueven al disquete para que se realice la operación de lectura - escritura , según las señales enviadas desde el controlador.

### SISTEMA DE LECTURA-ESCRITURA

Este bloque incluye el medio de grabación que en este caso es el disquete y la circuitería de lectura – escritura; una señal de control enviada desde el controlador determinará la operación de lectura o escritura; la cabeza de lecto-escritura es en esencia, una bobina capaz de concentrar fuerzas magnéticas sobre una pequeña área en la superficie de grabación.

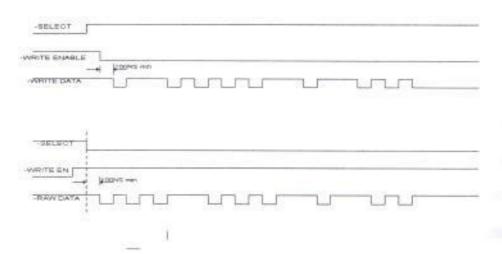

### 1.2.4.3 Diagramas de Tiempo

### ESCRITURA DE DATOS (Fig. 1.8)

La señal de control de lectura de datos ingresa desde el equipo a través del controlador; esta señal controla la escritura y la operación del borrado de túnel. Las señales que intervienen son las siguientes:

Fig. 1.7 Diagrama de Bloques del MRU.

- a) Select: permite escoger de entre cuatro líneas de dirección, en el caso de este dispositivo solo se usará la entrada select

0.

- b) Write data: son los datos a guardar en el disquete.

- c) Write Enable: Cuando está activa el modo de escritura se habilita y los datos son grabados en el disco flexible, en caso contrario no se hará la escritura de datos.

## LECTURA DE DATOS (Fig. 1.8)

La señal de control de lectura de datos es transferida desde el disk drive al controlador. Las señales que intervienen son las siguientes:

- a) Select: permite escoger de entre cuatro

líneas de dirección, en el caso de este

dispositivo solo se usará la entrada select

0.

- b) Write enable: Cuando está activa, el modo de lectura se habilita y los datos

son leídos desde el disco flexible, en caso contrario no se hará la escritura de datos.

c) Raw Data: Cuando esta señal es seleccionada, proporciona señales conjuntas de reloj y datos.

Fig. 1.8 Diagrama de Tiempo de Escritura y Lectura de Datos del MRU

### 1.2.4.4 Controlador del Disco Flexible (FDC)

Existen circuitos integrados que realizan todas las funciones necesarias para controlar un disco flexible, los FDC deben realizar una serie de funciones comunes:

a. Verificación automática.

- b. Compatibilidad de formatos.

- c. Generación y verificación del CRC (comprobación de redundancia cíclica).

- d.Lectura-escritura con: uno o mas bloques, búsqueda automática del sector, lecturaescritura completa de la pista.

- e.Control simultáneo de varias unidades de disco.

De cualquier manera el programador será el encargado de saber donde se almacena cada información del disco. Los controles programables son: el tiempo de paso de pista a pista, el tiempo de establecimiento del cabezal, el tiempo de enclavamiento del cabezal, control del motor de paso, transferencia DMA programada. El empleo de acceso directo a memoria es imperativo para todos los discos estándar ya que no hay ningún microprocesador que pueda trabajar con el programa con las velocidades de estos discos.

### 1.3 Dispositivos de Almacenamiento de Memoria:

En la actualidad encontramos en el mercado una infinidad de dispositivos de almacenamiento de memoria, entre los cuales tenemos:

### 1.3.1 Las Unidades de Disco Flexible:

El desarrollo de la unidad de disquete tuvo lugar en 1967 en el San José Lab., de la empresa IBM, estas unidades fueron inicialmente de lectura, para discos de 8" de diámetro, de una sola cara y con capacidad máxima de 100KB.

Luego, estas unidades fueron transformadas en sistemas de lectura y escritura con discos de dos caras, dando capacidades de hasta 250KB, luego se desarrolló una unidad que en ese entonces se denominó Mini-Disk, de 5.25", existente aún en el medio informático, aunque no con el mismo nombre.

Finalmente aparecieron las unidades de 3.5 pulgadas, actualmente de uso masivo en las computadoras. También han surgido en el mercado, aunque sin mucho auge, las unidades de 120 MB7, con capacidad de almacenamiento ochenta veces mayor utilizando la misma superficie de los discos tradicionales. Para organizar la información, el sistema operativo de la computadora durante el formateo de un disquete, divide su superficie en las pistas y sectores respectivos y adicionalmente asigna el espacio mínimo de almacenamiento denominado clúster. Las diferentes secciones de superficie en las que se divide un disco luego de ser formateado son:

- PISTA: Es la sección de la superficie correspondiente al área encerrada por dos circunferencias concéntricas.

- SECTOR: Es la sección de la superficie del disco que corresponde al área encerrada por dos lineas radiales de una pista. Siempre que se hace referencia a un sector, se tienen en cuenta cuántos de ellos son pistas.

Mega Bytes

CILINDRO: Es el conjunto de pistas que ocupan las mismas posiciones en diferentes lados del disco. En un disquete, un cilindro está formado por una de las pistas superiores y por la pista de la otra cara que queda exactamente debajo.

### 1.3.1.1 Cálculo de la Capacidad de un Disquete .

Se hace multiplicando la cantidad de caras del disco por los sectores contenidos en cada una de ellas y finalmente por la cantidad de bytes de cada sector. Por ejemplo, el cálculo hecho para conocer la capacidad de un disquete de 1.44 sería:

No. De caras: 2

No. De pistas por cara: 80

No. De sectores por pista: 18.

No. De bytes por sector: 512

Multiplicamos: 2 caras x 80 pistas x 18 sectores/pista = 2880 sectores.

2880 sectores x 512 bytes = 1.474.560 bytes, que corresponden a 1.44 MB.

### 1.3.1.2 Clúster o Unidad de Asignación

Es el conjunto de sectores utilizados por el sistema operativo como área mínima de almacenamiento. Un clúster está compuesto por determinada cantidad de sectores y no puede contener información perteneciente a varios archivos. Por ejemplo, en un disquete de 2.88 MB, cada clúster está compuesto por dos sectores (recordemos que cada sector puede almacenar hasta 512 bytes): Por lo tanto, en este disquete, un clúster puede almacenar hasta 1024 bytes. En los disquetes de 1.44 MB, un clúster es equivalente a un sector.

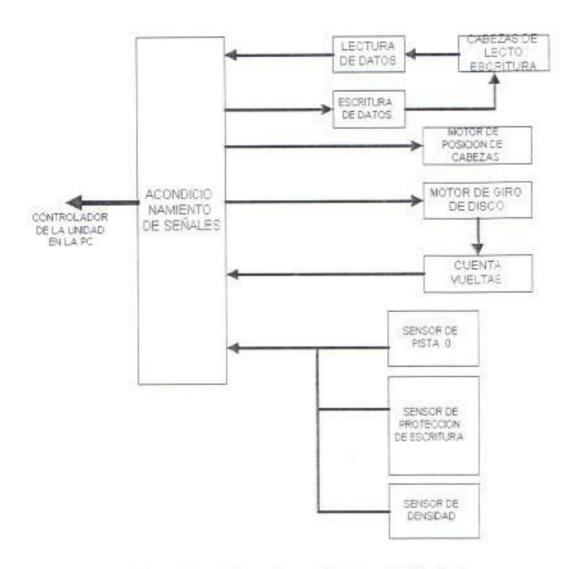

## 1.3.1.3 Funcionamiento de las Unidades de Disquetes.- Diagrama de Bloques:

En la figura 1.9 se observa el diagrama de bloques de una disquetera. Casi todos los

circuitos electrónicos que se encuentran dentro de la unidad, tienen como función principal el almacenamiento de señales, ya que el control es efectuado desde una tarjeta de interfase o desde la tarjeta principal de la computadora, donde se encuentra la circuitería denominada controlador de la unidad.

### 1.3.1.4 Sistemas Mecánicos:

a) Cabezas de lecto- escritura: La unidad fija la información a través de ellas sobre el disquete y a la vez puede recuperar los datos posteriormente. Para grabar las señales sobre el disquete, las cabezas deben generar un pequeño campo magnético de tal forma que polaricen el sentido de las particulas del disco de acuerdo al valor binario del dato

Fig. 1-9 Diagrama de bloques de una disquetera de 3.5 pulgadas.

La generación del campo magnético se hace a través de una bobina, la cual recibe el voltaje que representa el valor del dato, procedente de la circuitería de la unidad.

- b) Actuador de las cabezas: Para la lectura de la superficie del disco, las unidades poseen un motor que hace avanzar las cabezas en forma radial, desde el borde externo del disco hacia el centro del mismo y viceversa. El sistema encargado de esta labor es comandado por un motor de paso que da pequeños giros que luego, por medio de un sistema mecánico, son convertidos en pequeños desplazamientos de las cabezas sobre la superficie del disco.

- c) Motor de Giro: Por medio de un mecanismo de acople, la unidad adapta la parte central del disquete y la adhiere a un motor que la hace girar a una velocidad aproximada de 300 o 360 RPM: Esta velocidad depende del

tipo de unidad, siendo las de 5.25 de alta densidad las únicas que giran a 360 RPM.

d) También cuentan con un detector de pista cero, detector de protección contra escritura, detector de densidad de almacenamiento.

La tabla I nos muestra cada uno de los 34 pines de los que consta el interfase entre la disquetera y el equipo:

### 1.3.2 Las Unidades de Disco Flexible de 120 MB:

Con las unidades de 120 MB se dio un gran avance tecnológico en sistemas de almacenamiento en discos flexibles, ya que sobre la misma superficie, se pudo aumentar casi en 80 veces la cantidad de información almacenada. Para poder almacenar tanta información en un espacio tan pequeño, fue necesario reducir el tamaño de las pistas de los disquetes, con lo que aumentó el número de ellas en su superficie, pasando de 80 en un disquete tradicional a 180 en uno de este tipo.

| PIN    | SEÑAL                 | Entr/ Salida |  |

|--------|-----------------------|--------------|--|

| 2      | Escritura reducida    |              |  |

| 4      | WC (Write Conection)  |              |  |

| 6      | NC (No conectado)     |              |  |

| 8      | Indice                | S            |  |

| 10     | Habilita motor 1      | E            |  |

| 12     | Selección de unidad 2 | E            |  |

| 14     | Selección de unidad 1 | E            |  |

| 16     | Habilita motor 2      |              |  |

| 18     | Selección dirección   | E            |  |

| 20     | Paso                  | E            |  |

| 22     | Datos a escribir      |              |  |

| 24     | Habilita escritura    | Ε            |  |

| 26     | Pista 0 (Track 00)    | S            |  |

| 28     | Protección contra     | S            |  |

|        | escritura             |              |  |

| 30     | Dates unides          | S            |  |

| 32     | Selecciona lado 1     | E            |  |

| 34     | Cambio de disquette   | S            |  |

| mpares | Tierra                |              |  |

Tabla II Distribución de Pines de la disquetera de 3.5"

Para que las cabezas se pudieran ubicar correctamente en pistas tan delgadas, se diseñó un sistema óptico que

suministra información precisa del sitio exacto donde se está leyendo o guardando datos.

Gracias a este sistema óptico que trabaja por medio de láser, las unidades LS-120 no necesitan motor de paso como sucede con las unidades tradicionales. Adicionalmente no necesitan identificar la pista cero.

### 1.3.3 Memorias SRAM:

Las memorias RAM ESTÁTICAS, son un dispositivo de almacenamiento de memoria muy utilizado en la actualidad por su rápido tiempo de acceso, por su disponibilidad en el mercado y por las características operacionales que presentan; este tipo de memoria necesita de alimentación para funcionar y guardar los datos, pues con el control de ciertas señales puede leer, escribir o permanecer en alta impedancia a la espera de que las señales nuevamente se presenten.

El NS-9010 utiliza un banco de memorias SRAM 7188L70CBX (ver Anexo 1)

#### 1.3.4 Memorias EPROM:

Las memorias EPROM son una alternativa económica, manejable y funcional para aplicar la técnica de disk on chip, es decir, para almacenar microinstrucciones cuando el programa no es muy extenso.

También son utilizadas en la mayoría de controladores para diseños digitales, tienen la propiedad de guardar información sin necesidad de tener alimentación, y que pueden ser borradas por medio de un tratamiento de luz ultravioleta.

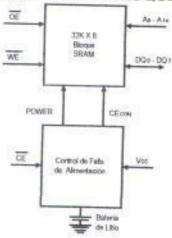

#### 1.3.5 Memorias NVSRAM:

Estas memorias son en si una innovación tecnológica que combina dentro del integrado una memoria SRAM y una fuente de alimentación de 5v DC, de este modo el circuito de control monitorea constantemente la alimentación de la memoria, de manera que si existe una interrupción de alimentación, inmediatamente la fuente interna pasa a suplir el voltaje y con esto la información almacenada no se pierde. El chip consta del integrado y una fuente de poder de litio proporciona la combinación de una memoria

no volátil con las características de ciclos de escritura ilimitada de las SRAM estándar.

El circuito de control controla constantemente la alimentación de 5v hasta ciertos parámetros de tolerancia, cuando no se produce esa alimentación, la SRAM se protege incondicionalmente contra escritura para prevenir cualquier operación de escritura inadvertida. En este momento, la energía de la fuente provee la alimentación necesaria para mantener la información de la memoria hasta que retorne la alimentación externa. Las memorias NVSRAM no requiere circuitería externa y es compatible con los sockets (calzos) de las SRAM estándar y la mayoría de EPROM y EEPROM<sup>6</sup>.

Cuando la alimentación se suspende, las SRAM se protegen automáticamente contra escritura, todas las salidas se ponen en alta impedancia y todas las entradas son consideradas como "dont care" (sin importancia). Si un acceso válido está en proceso al momento de que se produzca una falla de poder, el ciclo de memoria continúa

Electrical Erasable Prom; Memorias que se borran eléctricamente.

hasta completarse. La batería interna de estas memorias proporciona una retención de datos por el lapso de 10 años en ausencia de voltaje de alimentación.

# **CAPÍTULO 2**

## 2 ANALISIS DEL PROBLEMA

### 2.1 Situación Actual del Equipo

### 2.1.1 Proceso de Almacenamiento del Programa Operativo.

Una vez que el equipo es encendido, el sistema verifica si el programa operativo se encuentra residente en memoria, caso contrario permanece en stand by (alta impedancia) hasta que el operador pulse el botón *PRGM LOAD* que se encuentra en el tablero control, el MRU lee el disquete de 8 pulgadas y transfiere la información al banco de memorias, de esta manera el equipo está listo para realizar sus funciones.

El banco de 128K utiliza 32 memorias SRAM 7188L70DB de la marca IDT que necesitan estar alimentadas para

conservar la información guardada en ellas, de lo contrario los datos se pierden y al encender nuevamente el equipo, se necesitará cargar el Programa Operativo . Para aprovechar esta propiedad, el equipo cuenta con una circuitería propia de alimentación entre un banco de baterías localizadas en la gaveta PSU y los pines de alimentación del banco de memorias, permitiendo que una vez que el equipo se apaga, las memorias pasen al modo standby (alta impedancia) de acuerdo a la siguiente tabla;

| -CS | -W | DnN      | Mode    |  |

|-----|----|----------|---------|--|

| Н   | Х  | Hi-Z     | Standby |  |

| L   | Н  | Data-out | Read    |  |

| L   | L  | Data-in  | Write   |  |

Tabla II Lectura y Escritura de las memorias SRAM

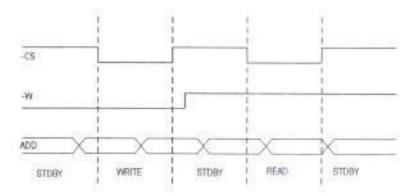

## 2.1.2 Ciclo de Escritura y Lectura

Para que las memorias cumplan con el ciclo de escritura, debe estar presente la dirección escogida (ADD 0-15), la señal W.L (write) debe estar en bajo y la señal CS.L también se debe encontrar en bajo, una vez que estas condiciones se cumplen, la información se escribe en las memorias.

Fig 2.1 Ciclo de Escritura y Lectura de las memorias SRAM

En cambio, en el ciclo de lectura las señal W.L debe ser alta y la señal CS.L debe encontrarse en bajo, una vez que esto se cumpla las memorias se leen en la dirección (ADD0-15) previamente establecida.

Tanto para la lectura como para la escritura, las memorias deben pasar por el modo STDBY, es decir, deben tener un tiempo de estabilización para variar de un ciclo a otro. El banco de memorias está organizado en grupos de cuatro componentes , por lo tanto existirán ocho unidades de memoria de 16K con palabras de 16bits. La transferencia

de datos desde y hacia la memoría se desarrolla a través de buses de 16bits, es decir, cuatro memorias leerán o escribirán la información al mismo tiempo en una dirección escogida, por lo tanto cada unidad de memoria actuará como una sola de 16K por 16bits.

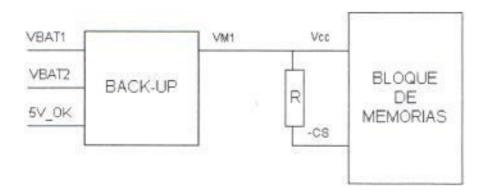

## 2.1.3 Diagrama Eléctrico de Alimentación de las Memorias

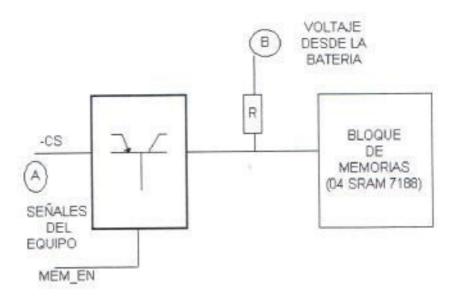

El diagrama de bloques que proporciona la información de la conexión eléctrica de las baterías con el banco de memoria, se presenta en la figura 2.2.

De esta manera se observa el modo como interactúan las baterías, el banco de memorias y el equipo para mantener el Programa Operativo cargado en el banco de memorias. Las baterías alimentan a las memoria en el pin Vcc (22) y envian una señal alta a -CS (10) para que permanezcan en el modo standby mientras el equipo esté apagado.

Fig 2.2 Diagrama de bloques de la alimentación eléctrica de las memorias

De acuerdo a lo observado en el diagrama de bloques, la alimentación en Vcc y el control de –CS se produce por medio de dos fuentes: la alimentación desde el equipo (5V, 60 amp.) y la alimentación desde las baterías (3.7voltios, 14.5 amph.) Para los procesos de lectura y escritura es necesario controlar a –CS, de lo contrario las memorias se mantendrían todo el tiempo en alta impedancia (standby).

Para mantener el control de -CS de las memorias, el equipo utiliza la siguiente configuración eléctrica particular, que se podría denominar maestro-esclavo. En el gráfico (2.3) se ha representado el comportamiento eléctrico de una unidad de memoria, que es el mismo para las unidades restantes. Las señales que llegan a -CS desde el equipo provienen desde A a través de un banco de transistores, la señal alta que proporciona la batería proviene desde B a través de una resistencia R; cuando el equipo está encendido, las señales altas y bajas de -CS son enviadas desde el sistema, la señal alta de la batería cae en la resistencia R, por lo tanto las señales dominantes serán las que provienen desde A (maestro), sin importar la señal alta permanente en B.

Cuando el equipo se apaga no se tienen señales enviadas desde el equipo, por lo que inmediatamente será B (esclavo) quien envíe la señal alta al banco de memorias, garantizando de esta manera un funcionamiento en los modos de lectura, escritura y standby cuando el equipo está encendido y únicamente en standby cuando el equipo está apagado.

Fig. 2.3 Configuración Eléctrica maestro-esclavo del banco de memorias SRAM

### 2.2 PLANTEAMIENTO DEL PROBLEMA

El Escuadrón de Lanchas Misileras (ESCLAM) está conformado por tres unidades: LAE QUTO, LAE GUAYAQUIL y LAE CUENCA, todas equipadas con el sistema de Guerra Electrónica NS-9010-EC; actualmente la LAE QUITO no cuenta con la unidad MRU (Magnetic Recorder Unit), por lo tanto, no puede cargar el Programa Operativo y por ende el equipo no puede operar. Cuando la LAE QUITO tiene que cumplir una operación, necesita que una de las otras Lanchas Misileras le facilite el MRU para poder operar el equipo.

El Programa Operativo está almacenado en disquetes de 8 pulgadas, formateados bajo un Sistema Operativo desconocido, los mismos que se están deteriorando rápidamente, con lo que se calcula que en mediano plazo ninguna Lancha Misilera tendrá en su poder un disquete de cargado para poner a funcionar los equipos.

Las memorias SRAM con que cuenta el equipo no poseen alimentación de respaldo, pues su original del equipo consistía en dos baterías marca TADIRAN de 3.7v. que se agotaron hace aproximadamente 3 años, y permitían que el Programa Operativo permaneciera residente en memoria aún cuando el equipo estuviera apagado. Una vez realizado el análisis del problema, en la tabla III se definen los efectos y consecuencias de estos problemas.

Una vez determinadas las causas, efectos y sus consecuencias, podemos enfocar al problema como la recuperación de:

- Capacidad Operativa de la Unidad.

- Operatividad del Equipo.

|      | CAUSA                                                                                                                             |   | EFECTO                                                                                      |   | CONSECUENCIAS                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------|

| ٠    | La LAE QUITO no cuenta con su MRU.                                                                                                | • | El Programa Operativo<br>no se puede cargar                                                 | • | El equipo no realiza<br>ninguna función.                                                                                                       |

| •    | Disquettes de 8 pulgadas donde se almacena el Programa Operativo deteriorándose rápidamente.                                      | • | El Programa Operativo corre el riesgo de desaparecer de sus dispositivos de almacenamiento. | • | Pérdida paulatina de la capacidad operativa de la unidad y de la operatividad del equipo, hasta llegar en el mediano plazo a la pérdida total. |

| •    | Préstamo de MRU entre Lanchas Misileras para cumplir operaciones.                                                                 | • | Si las tres Lanchas salen<br>a cumplir una operación,<br>una de ellas se queda sin<br>MRU.  | • | Pérdida de la capacidad<br>operativa de una de las<br>unidades, en este caso<br>de la LAE QUITO.                                               |

| • 12 | Carga repetitiva del programa operativo debido a la ausencia de alimentación de respaldo en el Banco de memorias SRAM del equipo. | • | El sistema no aprovecha sus prestaciones.                                                   | • | El MRU se deteriora.  Los disquetes sufren  desgaste de sus pistas  magnéticas por el  exceso de uso:                                          |

Tabla III Tabla causa-efecto-consecuencias

### 2.2.1 Capacidad Operativa de la Unidad

Se entiende como Capacidad Operativa a la eficiente disponibilidad, a la aplicación de los medios y recursos que posee una unidad para el cumplimiento de la tarea encomendada; en el caso que nos concierne, debido la la ausencia del MRU la LAE QUITO ha disminuido considerablemente su capacidad operativa, dependiendo del préstamo del MRU de las otras Lanchas; es imperativo entonces buscar los medios necesarios para que esta unidad recupere su capacidad operativa mediante el aprovechamiento y la modificación de las características de los bloques que intervienen en la carga del Programa Operativo.

## 2.2.2 Operatividad del Equipo

Es la medida de la posibilidad de utilizar todas las prestaciones que el equipo ofrece al usuario; por el momento el NS-9010 no tiene un buen grado de operatividad pues la ausencia del MRU, así como el deterioro del los disquetes y la ausencia de alimentación de respaldo comprometen el Proceso de Carga del Programa Operativo.

# CAPÍTULO 3

## 3 ALTERNATIVAS DE POSIBLES SOLUCIONES

## 3.1 Recuperacion de la Capacidad Operativa de la LAE Quito

La posible solución es el diseño de un circuito de carga de una batería recargable que proporcione la alimentación necesaria para poner al banco de memorias SRAM del NS-9010-EC en el modo standby (alta impedancia) cuando el equipo esté apagado y que recargue la batería cuando el sistema se encuentre en operación, de esta manera tendremos el programa Operativo residente en memoria aún cuando se apague el equipo.

### 3.2 Recuperación de la operatividad del NS-9010-EC

El programa operativo del equipo es un software almacenado en un disquete de 8 pulgadas, que realiza las funciones de operación del NS-9010-EC. Sin el programa operativo, el equipo pierde completamente su capacidad de operación, es decir, no realiza función alguna de detección, procesamiento, presentación en pantalla y análisis de las señales de radio-frecuencia; por lo tanto la búsqueda de posibles soluciones se centra en dos puntos fundamentales:

- Levantamiento de la Información del programa operativo del equipo (SOFTWARE).

- Diseño del nuevo dispositivo de almacenamiento del programa operativo (HARDWARE).

Es importante acotar que la solución en software (levantamiento de la información de Programa Operativo) es el principal condicionante para aplicar posteriormente el diseño del Hardware; de nada serviria el diseño de un interfase con una disquetera de 3.5 pulgadas o un CDROM ,por ejemplo, si aún no hemos recuperado el Programa Operativo.

Entonces, es imperativa la manera como se logre recuperar la información para los futuros diseños, a continuación se analizarán

las fuentes a donde podemos recurrir para aplicar la solución en software:

### 3.2.1 Levantamiento de Información del Programa Operativo

El programa operativo se lo encuentra en tres formas, desde donde se intentará recuperarlo:

- Disquete de 8 pulgadas.

- Programa Fuente.

- Banco de memorias del equipo (una vez que se carga el sistema operativo desde el disquete).

## 3.2.1.1 Desde el Disquete de 8 pulgadas

Se considera como la primera y principal opción para lograr obtener la información del Programa Operativo del equipo.

El NS-9010-EC NO presenta ningún tipo de directorio ni subrutina en pantalla, el equipo únicamente presenta las utilidades propias para la operación del equipo; por tanto, para recuperarlo por esta via será necesario tratar de

controlar la disquetera de 8 pulgadas por medio de una PC convencional, preferentemente una 486, por la velocidad del procesador y tratar de migrar la información a otro dispositivo de almacenamiento.

La disquetera de 8 pulgadas salió del mercado hace 20 años aproximadamente, las PC actuales no tienen los conectores para instalar directamente la unidad, es necesario realizar un interfase o un cableado equivalente entre los 34 pines de las disqueteras de 3.5 pulgadas y los 50 pines que controlan a la disquetera de 8 pulgadas.

El control vía hardware de la disquetera sí es posible, tomando ciertas precauciones y previsiones en la equivalencia de pines de las disqueteras actuales que tienen 34 pines y las de 8 pulgadas que poseen 50 pines.

Las pruebas realizadas en laboratorio confirman el concepto teórico referenciado anteriormente, es decir, una disquetera de 8 pulgadas puede ser controlada por una PC bajo DOS, lamentablemente nuestro caso es diferente porque el disquete no está formateado bajo este Sistema Operativo.

En cuanto a software, el Programa Operativo no está bajo DOS.

Es decir aún solucionando la dificultad de compatibilidad de hardware nos encontraremos con la novedad de que una PC no reconocerá ni formateará ningún disquette. Se han realizado contactos con la empresa fabricante y han proporcionado informaciones escuetas e imprecisas sobre el sistema operativo bajo el cual funcionan sus discos.

## 3.2.1.2 Desde el Programa Fuente

Es necesaria la transcripción integral del programa fuente por medio de una PC y luego compilarlo; y aún así, se debería conocer el Sistema Operativo bajo el cual están formateados y grabados los discos. Además existe la incertidumbre de que existan ciertas subrutinas ocultas.

#### 3.2.1.3 Desde el Banco de Memorias

Por medio de un interfase entre una PC y el banco de memorias, además de un software que controle a las memorias y las pase del estado STDBY (alta impedancia), al estado de lectura (READ) a través de una tarjeta de adquisición de datos. El banco de memorias proporcionará la información binaria del Programa Operativo sin importar el formato bajo el cual se grabó la información.

## 3.3 Diseño del Nuevo Dispositivo de Almacenamiento de Memoria Está intimamente ligado con la forma como se recupere la información del programa operativo del equipo, por lo que se presentan las siguientes opciones:

DISPOSITIVO PERIFERICO (DISQUETERA DE 3.5 PULGADAS-CD ROM - UNIDAD 120 MB): Se utilizará este dispositivo si el programa se recupera desde el disquete de 8 pulgadas o se lo compila desde el programa fuente; su implementación requiere una modificación de la tarjeta de interfase entre la disquetera y el equipo, así como también un bus equivalente para la instalación física de la disquetera nueva.

3

La información guardada en el disquete de 3.5 pulgadas deberá ser una fiel reproducción de la información original, es decir, deberá estar bajo el mismo sistema operativo, por lo tanto ningún otro equipo comercial lo reconocerá.

BANCO DE MEMORIAS: Se conoce como la técnica DISK ON CHIP<sup>9</sup>, se la utiliza cuando se desea guardar programas pequeños en un determinado número de memorias, especialmente EPROM. Es aplicable en caso de recuperar la información directamente desde el banco de memorias. No será necesaria la modificación de la tarjeta interfase pues se aprovecha el modo de inicialización del equipo (chequeo del programa operativo en las memorias).

Disquete en integrado: Técnica muy utilizada en la actualidad, se refiere al grabado de programas operativos de tamaño menor en memorias (ej. EPROM, NVSRAM)

#### 3.4 Solución Planteada

Una vez analizadas cada una de las posibles soluciones, tomando en cuenta su tiempo de desarrollo ,ventajas, desventajas y grado de confiabilidad, se plantea la siguiente solución:

- Recuperación de la información desde el banco de memorias por medio de un software que simule el control de las memorias y un hardware que realice un barrido de direcciones y almacene los datos que envíen las memorias al momento de ser leídas.

- Diseño de un banco de memorias EPROM paralelo, de modo que almacene la información del Programa Operativo (disk on chip), por lo tanto, si se produce una falla de alimentación en las memorias y el programa operativo se pierde, lo único que se debe hacer es cargarlo desde este dispositivo paralelo al banco de memorias del equipo.

# **CAPÍTULO 4**

## 4 DISEÑO DEL PROTOTIPO RESPALDO DE BATERIA

#### 4.1 Batería Recargable

La batería, es la fuente de corriente eléctrica de emergencia más segura para los equipos que se alimentan de corriente continua, pues, al ser cargada, acumula energía eléctrica almacenada en forma de energía química; y al descargarse, la energía química vuelve a convertirse en energía eléctrica.

Existen baterías de plomo y níquel- cadmio, con manufactura y propiedades diferentes, siendo las primeras las más utilizadas especialmente en sistemas de telecomunicaciones.

En razón de sus diferentes propiedades eléctricas ,las baterias de plomo pueden subdividirse en:

- Baterías para carga de corta duración (carga capacitiva menor de 1 hora).

- Baterías para cargas de larga duración (carga capacitiva mayor de 1 hora).

Además de las baterías de plomo normales, existen baterías de plomo cerradas que no necesitan de mantenimiento y que se distinguen del tipo convencional por el uso de un electrolito establecido y por el empleo de aleaciones libres de antimonio. Estas nuevas baterías de plomo han sido introducidas al mercado bajo la denominación *DRYFIT*. Estas baterías no están equipadas con los clásicos tapones, sino con válvulas de seguridad que se abren en el caso de presión excesiva.

### 4.1.1 Proceso de Descarga

Si se unen ambos electrodos mediante una resistencia, comienza a circular una corriente (I), durante este proceso tiene lugar la conversión química de la masa activa de ambas placas.

Debido a los procesos electro químicos que suceden durante la descarga, tanto el dióxido de plomo de la placa positiva, como el plomo de la placa negativa se convierten en sulfato de plomo (PbSO<sub>4</sub>), donde también se consume ácido (H<sub>2</sub>SO<sub>4</sub>) y se forma agua (H<sub>2</sub>O); como resultado, disminuye la concentración del ácido de manera proporcional a la energía consumida; en un principio, la descarga produce una disminución lenta de la tensión, que se vuelve más rápida hasta llegar a un valor límite inferior (denominada tensión final de descarga), establecido de acuerdo a la intensidad de la corriente de descarga.

Al mismo tiempo que se producen todos estos cambios químicos, se produce también un fuerte aumento de volumen, debido a que los poros de la masa comienzan a taponarse y a obstaculizar el ingreso de ácido a las partículas interiores de la masa, esta situación irregular produce una disminución del ritmo de la reacción y declinación de la conductividad, produciéndose una drástica reducción de la tensión de descarga hasta llegar a valores inferiores a la tensión de descarga establecida.

#### 4.1.2 Proceso de Carga

Al conectar la batería descargada a una fuente de corriente continua, es posible recargarla, siempre y cuando la tensión de la fuente de corriente continua sea superior a la de la batería.

Durante el proceso de carga, la masa activa de ambos electrodos y el ácido sulfúrico se reconvierten al estado original existente antes de la descarga; es decir, se desarrolla exactamente el proceso inverso de la descarga. Debido a que el material de las placas se vería a la larga deteriorado por la constante repetición de este proceso, es importante que, una vez alcanzada la tensión de gasificación, la intensidad de la corriente de carga no pueda superar determinados valores, debiendo ser reducida en caso de necesidad. El valor admisible de la intensidad de la corriente al llegar al punto de gasificación depende de la construcción de los elementos y del método de carga.

#### 4.1.3 Tensión de Reposo

Denominada también FUERZA ELECTROMOTRIZ (FEM), no es otra cosa sino la tensión de reposo de la bateria NO sometida a descarga, la misma que depende directamente de la densidad del ácido. Cuanto mayor es la FEM, tanto más alta es la tensión de reposo: en la práctica, es suficiente saber que la tensión de reposo es aproximadamente igual al valor de la densidad nominal del ácido más 0.84.

#### 4.1.4 Tensión Nominal

En la batería de plomo la tensión nominal se hace efectiva poco después de comenzar la descarga, cuando se ha equilibrado el ácido interior y exterior.

#### 4.1.5 Tensión de Descarga

La tensión durante la descarga depende de:

- · La intensidad de la corriente de descarga; y,

- El tiempo.

Cuánto más elevada sea la corriente de descarga y cuanto más dure el tiempo, tanto más baja será la tensión de descarga. La causa de este proceso se explica con la disminución de la densidad del ácido y en consecuencia de la fuerza electromotriz, así como con la caída adicional de la tensión por efecto de la resistencia interior.

Un parámetro para evaluar el estado de descarga de la batería lo brinda la relación Tensión de Descarga vs. Intensidad de Corriente, indicada en las curvas de descarga propias de cada batería.

Al comenzar la descarga, la tensión pasa por un punto mínimo, al que denominamos bolsón de tensión; una causa de la breve declinación de la tensión al comenzar la descarga es la demora transitoria en la aparición de iones sulfato de plomo. Debido a este desarrollo inconstante se indica como tensión inicial de descarga a aquellos valores medidos después de extraer el 10 por ciento de la capacidad correspondiente a la respectiva corriente de descarga.

El desarrollo de la tensión, una vez superado el bolsón de tensión, es aproximadamente proporcional a la declinación

de la densidad del ácido; es decir, la tensión declina proporcionalmente a la curva de descarga característica de la respectiva batería.

Al continuar la descarga, la curva toma sus valores en función de los problemas de difusión, emprobrecimiento del material activo y disminución de la conductividad, esta es la razón por la cual la tensión disminuye muy rápidamente hacia el final de la descarga y que de un elemento se puede extraer tanta menor capacidad hasta alcanzar la tensión final de descarga cuanto más alta es la corriente de descarga. Así es como la capacidad extraíble declina aproximadamente 50 por ciento cuando en lugar de una corriente de descarga de 10 horas se tiene una de 1 hora.

# 4.1.6 Tensión Final de descarga y Tensión Final en función del sistema

Es aquella tensión por debajo de la cual no se puede pasar al producirse la descarga con la corriente asignada; pues, de lo contrario existe el peligro de que el sulfato de plomo no se reconstituya químicamente; y, que en

consecuencia, descienda fuertemente la eficiencia de la batería; o que en caso de frecuentes descargas por debajo de la tensión final de descarga, se afloje o deteriore la estructura de la masa activa en las placas debido al cambio de volumen.

Por esta razón, al producirse frecuentemente tensiones de descarga inferiores a la tensión de descarga final, la vida útil de las batería disminuye perceptiblemente.

La tensión final de descarga no debe confudirse con el limite inferior de tensión admisible por el sistema, pues este último se refiere al valor de tensión mínimo con el que el equipo opera con todas sus capacidades, este valor también se lo conoce como tensión final en función del sistema.

#### 4.2 Especificaciones generales del diseño

El prototipo debe cumplir con las siguientes:

De acuerdo al programa de mantenimiento preventivo, el NS-9010-EC debe encenderse semanalmente, por lo tanto la batería del equipo tiene que alimentar sin interrupción al banco de memorias por un lapso mínimo de 15 días.

- El Sistema no debe percatarse del cambio, por tanto, las señales, voltajes y corrientes de respuesta que generan los módulos vecinos desde y hacia el equipo, no deben sufrir ningún tipo de alteración.

- La alimentación del prototipo se tomará de una de las fuentes de 5Vdc con que cuenta el equipo.

#### 4.3 Dimensionamiento de la Bateria

#### 4.3.1 Capacidad:

Es una medida de su eficacia y tamaño, se mide en Amperios-hora e indica la cantidad de energía que una batería está en condiciones de suministrar al descargarse con una corriente constante (A) hasta alcanzar una tensión preestablecida, en un tiempo determinado (h).

#### 4.3.2 Rendimiento y Factor de Carga:

Rend. En amp-hora= amp-h en Ah extraidos. / amp-h en Ah suministrados.

Rend. En vatios-hora= vat-h en Wh extraídos / vat-h en Wh suministrados.

Ambas magnitudes dependen de la construcción del elemento, de la temperatura del ácido y del valor de la corriente de carga o descarga.

Bajo factor de carga se entiende el valor recíproco del rendimiento en amperios-hora, el más usual es:

F. carga= amp-h en Ah suministrados / amp-h en Ah extraidos

Por lo general el Factor de Carga de las baterias recargables convencionales es de 1.1 a 1.2.

## 4.3.3 Análisis de parámetros del Banco de Memorias:

De acuerdo a las especificaciones de las memorias SRAM utilizadas, y al análisis de capítulos anteriores, el banco de memorias necesita de una corriente de 12.8 mA y un voltaje en el intervalo de 3.7-5 v para mantenerse en la condición alta impedancia (STDBY). Teniendo en cuenta las especificaciones generales del diseño y los conceptos

de capacidad, la batería se dimensiona del siguiente modo:

(12.8 mA \* 15 dias \* 24 horas) / 1 dia

- = 4608 mAh

- = 4.608 Ah

- = 5 Ah

El proceso de carga de la batería se produce siempre que la tensión de la fuente de corriente continua sea superior a la de la batería. Por lo tanto se instalará una batería de:

- Voltaje 4 V.

- Capacidad 5 Ah.

- Tipo DRYFIT

Que alimentará al banco de memorias cuando el equipo esté apagado.

## 4.3.4 Análisis de recarga de la Bateria:

Al trabajar en régimen de carga de mantenimiento, la batería va recibiendo constantemente una pequeña corriente en el rango de los mA. Por cada Ah. De capacidad nominal. Esta corriente de carga se produce cuando se aplica a las elementos una tensión estable de +5 Vdc.

Si se observan las instrucciones indicadas para el tratamiento de las baterías, estas podrán ser operadas durante la totalidad de su vida útil con una tensión de carga de mantenimiento.

No es necesario limitar la corriente de carga admisible para la batería hasta alcanzar la tensión de gasificación (carga completa). Sin embargo, cuando la temperatura del electrolito se eleva más allá de 55° C es necesario interrumpir la carga.

El circuito de respaldo de batería será quien cargue las baterías de acuerdo a las curvas características de la batería escogida. Este proceso tiene lugar en dos etapas: en primer lugar la corriente de carga permanece constante al ir aumentando la tensión de carga hasta que según la línea característica de la batería seleccionada, haya sido alcanzada la tensión específica. A partir de este valor la tensión es mantenida constante y en consecuencia la carga tiene lugar con corriente que declina hasta valores bajos.

#### 4.4 Desarrollo del Prototipo

1161

#### 4.4.1 Implantación

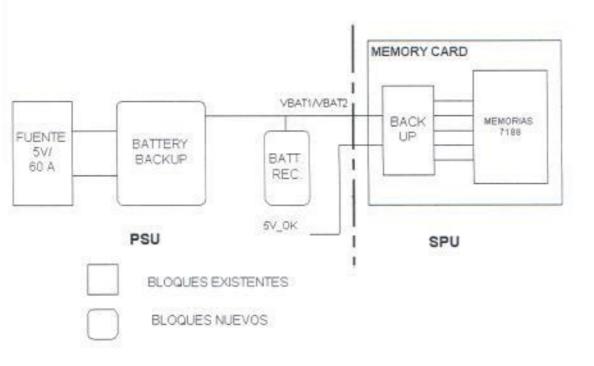

En la figura 4.1 se presenta en diagrama de bloques la implantación de el circuito de respaldo de batería y su relación con los elementos instalados, en lo posterior se explica brevemente cada uno de los bloques

Fig. 4-1 Diagrama de bloques de la implantación del prototipo

#### 4.4.1.1 Fuente B:

El equipo tiene dos fuentes gemelas de +5Vdc (A y B), se escogió la fuente B porque es la que soporta menor carga, a pesar de que por su diseño y dimensionamiento, el dispositivo de respaldo de batería es casi despreciable para la fuente.

#### 4.4.1.2 Circuito respaldo de Bateria:

Es el dispositivo que permitirá la carga de la batería cuando esté alimentado, mientras que cuando no esté alimentado, se opondrá a que la corriente de la batería retorne hacia la fuente (circuito abierto) sino más bien que alimente al banco de memorias para mantenerlas en alta impedancia (STDBY).

### 4.4.1.3 Batería Recargable:

Será la encargada de alimentar al banco de memorias cuando el equipo esté apagado y se recargará cuando se encienda.

#### 4.4.1.4 Backup:

Es un bloque que pertenece a la tarjeta de memoria, recibe la alimentación tanto de la batería, como del sistema, generando los voltajes (VM1,VM2,VM3, VM4,MEM\_EN) que alimentan a Vcc y -CS de las memorias. Por medio de un circuito de transistores que actúan a modo de interruptores electrónicos.

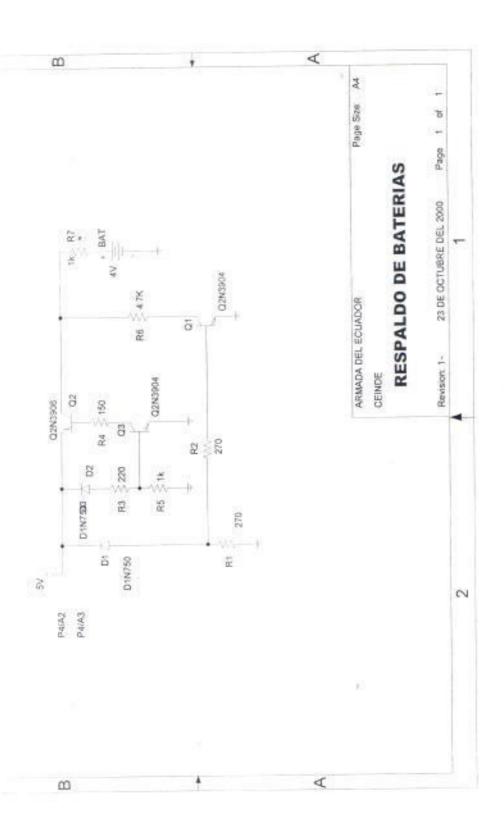

#### 4.4.2 Circuito respaldo de Batería.- Diagrama Eléctrico

En el Anexo 2 se encuentra un circuito que se adapta a las especificaciones del diseño y que cumple con los requerimientos operativos de la unidad y operacionales del equipo.

#### 4.4.3 Instalación

Las baterías originales estaban instaladas en el PSU y se conectan únicamente con el banco de memorias a través de la circuitería interna propia del equipo. El nuevo circuito tomará la alimentación desde el bloque PS2 (Power Suply 2) que provee +5v, que cumple con los valores calculados

en el dimensionamiento de las baterías para la recarga de las mismas.

#### 4.4.4 Operación del Circuito

Cuando se enciende el equipo, la fuente PS2(B) de 5v, 60

A alimentará a la tarjeta BATTERY BACKUP a través de los pines P4/A2 y P4/A3, la configuración D1-R1 en serie actúa como un regulador de voltaje, los transistores Q2 y Q3, el diodo D2 y las resistencias R3, R4 y R5 trabajan a modo de regulador de corriente, pues mantiene una corriente fija a través de la batería para variaciones en el voltaje terminal. El transistor Q1 se polariza a través de la resistencia R2 y permite que cualquier exceso de corriente sea canalizado a tierra. La batería se carga a través de R7 y la alimentación hacia el circuito VBAT1 y VBAT2 se lo realiza desde el colector de Q1, la misma que llegará hasta el bloque backup de la tarjeta de memoria de 128K.

Cuando el equipo se apaga, no habrá voltaje para que el Zener D1 esté activo, por ende no existirá voltaje en la base Q1 y el transistor (abierto), sucede el mismo caso con Q3, por lo que la batería será quien suministre la alimentación pues el circuito queda reducido a la batería R6 y R7 en serie.

Al prender nuevamente el equipo, Q1 se polariza y Q3 inmediatamente pasa a la zona de saturación (corto), permitiendo que la batería reciba carga desde el sistema y comience su operación de recargado.

#### 4.4.5 Localización

El circuito de respaldo de batería estará localizado en la gaveta PSU(Power Supply Unit) ocupando el lugar de las batería originales.

#### 4.4.6 Lista de componentes

- 02 diodos ZENER ½ W. 1N748A

- 02 Transistores NPN-Si AF/RF 5 W. 2N2222

- 01 Transistor PNP-Si Pwr. Amp. 2N4920

- 02 Resistencias 270Ω ¼ w.

- 02 Resistencias 150 Ω ½ w.

- 01 Resistencia 150 Ω ½ w.

#### 4.5 Selección de la Batería

En el mercado existen una infinidad de baterías recargables, de acuerdo a las especificaciones del diseño requerimos una batería o un banco de baterías de 4v 5 Ah.

## CAPÍTULO 5

# 5 DESARROLLO DEL PROTOTIPO RESPALDO DE MEMORIA

## 5.1 Especificaciones Generales del Diseño

- Realiza las mismas funciones que la tarjeta anterior, es decir, la operación no sufre alteraciones, las señales con las que interactúa con el sistema son las mismas antes y después de la modificación.

- Se sujeta al tiempo de ciclo del CPU, realiza el intercambio de datos a la velocidad establecida por el sistema.

- Una vez que el prototipo sea instalado, el bloque correspondiente al ingreso de datos desde el MRU no realiza ninguna función, salvo el caso de que por motivos de

mantenimiento se desee ingresar información por este medio.

La entrada de la disquetera será entonces un puerto auxiliar del

CPU.

- Debe aprovechar que el primer direccionamiento del sistema para buscar el Programa Operativo lo hace hacia el banco de memorias; si en este sitio no lo encuentra, entonces espera la presencia de una señal (PGM LOAD) para cargarlo desde el MRU hacia el banco de memorias.

- Es el equivalente a un DOS en una PC comercial, es decir, se guarda toda la información del Programa Operativo en un banco de memorias EPROM.

- Se particiona en dos sub bloques, de tal manera que el que contenga las memorias NVSRAM pueda operar como lo hace normalmente el banco de memorias del equipo, sin necesidad de estar relacionado con el segundo.

#### 5.2 Diseño del Prototipo

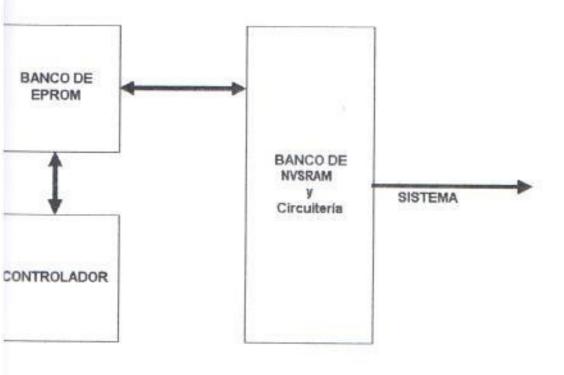

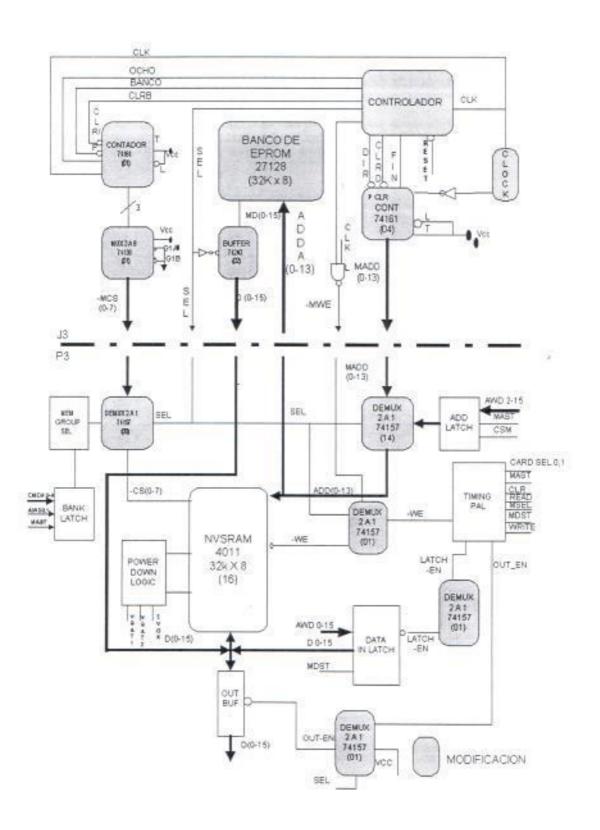

El prototipo consta de dos bancos de memorias:

- Banco de memorias NVSRAM, que reemplazarán a las SRAM que actualmente constituyen el banco de memorias del equipo, este banco de memorias proporciona una alta confiabilidad, pues al almacenar el Programa Operativo ya no será necesario realizar la carga del mismo.

- Banco de memorias EPROM, que reemplaza al bloque de cargado del Programa Operativo (Tarjeta Floppy Disk Interfase y MRU) utilizando la tecnología DISK ON CHIP, de modo que si por alguna razón el Programa Operativo del equipo se borra de las NVSRAM entonces se lo manda a cargar directamente desde el banco de memorias.

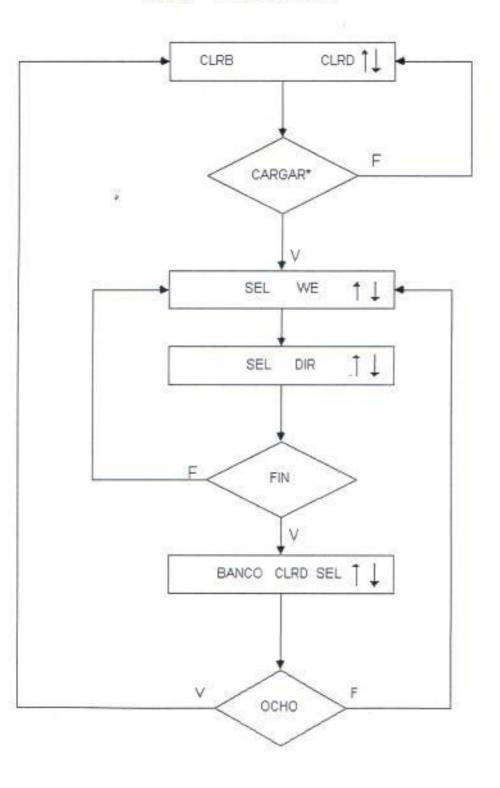

Al cargar el programa Operativo se leen las EPROM y se escriben las NVSRAM, es decir, es necesaria la presencia de un controlador que coordine las acciones de lectura por una parte y de escritura por la otra, las mismas que tienen que ser simultáneas y deben sincronizarse de acuerdo a la velocidad de las que están instaladas (SRAM). Es decir, el prototipo tendrá tres áreas bien definidas:

BANCO DE NVSRAM y CIRCUITERIA: Trabaja como la memoria del equipo, en reemplazo de las SRAM actuales, puede funcionar independientemente sin necesidad de los otros pues es prácticamente una modificación de la tarjeta actual del equipo.

BANCO DE EPROM: Trabaja como el reemplazo del bloque de cargado del Programa Operativo.

CONTROLADOR: Sirve de nexo y coordinación para la carga del Programa Operativo desde las EPROM hacia las NVSRAM, una vez realizada esta operación, el equipo no se percatará de la presencia de este sub-bloque, es decir nunca interactúa directamente con el sistema.

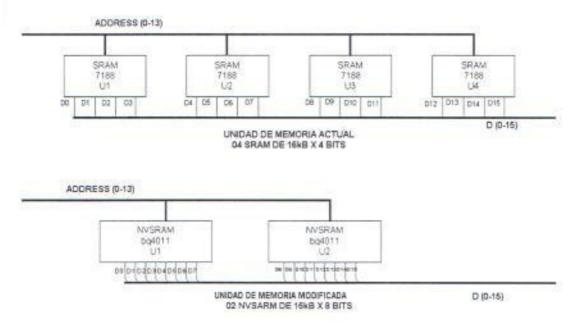

## 5.2.1 Elección de las NVSRAM para el Banco de Memorias

Para realizar una buena elección de las NVSRAM, se debe hacer una comparación de las características funcionales con las SRAM instaladas actualmente, si bien es cierto que no esperamos encontrar un reemplazo exacto, no es menos cierto que en el mecado existe un tipo de memoria que sea compatible con las SRAM actuales.

Fig 5.1 Diagrama de Bloques del Prototipo

De entre muchas marcas y modelos de NVSRAM, se ha escogido las Benchmarq bq 4011Y (Anexo 3) por las razones funcionales que se observan en las tablas IV, V, VI.

| CARACTERISTICAS                 | 7188                        | NVSRAM bq<br>4011Y          |

|---------------------------------|-----------------------------|-----------------------------|

| Tiempo de lectura-<br>escritura | < 70 ns                     | 150 ns                      |

| Tecnologia                      | CMOS                        | CMOS                        |

| Salida                          | TTL-COM                     | TTL                         |