# ESCUELA SUPERIOR POLITÉCNICA DEL LITORAL Facultad de Ingeniería en Electricidad y Computación

"DISEÑO Y CONSTRUCCIÓN DE UN PROTOTIPO BASADO EN FPGA Y SISTEMAS EMBEBIDOS, PARA CONTROLAR UN DISPOSITIVO DE MEDICIÓN DE NO2 EN CUERPOS DE AGUA Y ANALIZAR SUS RESULTADOS"

#### INFORME DE PROYECTO INTEGRADOR

Previo a la obtención del Título de:

**INGENIERO/A EN TELECOMUNICACIONES**

CASTILLO QUINTO EDGAR JAVIER

BRAVO LINO JORGE ALFREDO

**GUAYAQUIL - ECUADOR**

AÑO: 2019

#### **AGRADECIMIENTOS**

Agradezco a mis padres Edgar y Yolanda por siempre estar ahí cuando más lo necesitaba y estaba a punto de darme por vencido, por ser un ejemplo a seguir y darme sus consejos. A mis amigos que de alguna u otra manera me ayudaron en la elaboración de este proyecto. A los ingenieros Victor Arce y Nathaly Sanchez por su apoyo en todo momento y ayudarme a cumplir esta meta. A mi amigo y compañero de tesis Jorge por su trabajo duro y sacar el proyecto adelante.

#### Edgar Javier Castillo Quinto

Agradezco a DIOS por mostrarme siempre el camino a seguir ante las situaciones difíciles. A mi madre Efigenia Lino que soporto tanto y se esforzó para ayudarme a cumplir esta meta; también a mi padre José Bravo que siempre estuvo aconsejándome y apoyándome en todas las etapas de mi vida, tratando de darme ánimos cada día para seguir adelante. A Evelyn Arreaga guien hasta la escritura de este documento es mi compañera de vida y madre de mi pequeño hijo, por ser un apoyo, no solo emocional sino también económico, por saber entender los momentos difíciles que pasé y siempre tratar de cumplir todos mis caprichos, motivándome a salir adelante, y, por hacerme saber que se sentía orgullosa con cada paso que daba. A Kerly Ochoa, Christian Sacarelo, Rodrigo Castro, Daniel Ochoa, quienes conforman Byodinamics por confiar en mí y brindar su apoyo para la realización de este proyecto. A mi amigo y compañero de proyecto integrador, Edgar Castillo, porque fuimos un gran equipo de trabajo en cada proyecto que participamos, también, porque supo brindarme su apoyo en los momentos difíciles de mi vida. Por último, a mi pequeño hijo Elian Bravo que con solo una sonrisa y un abrazo lograba darme fuerzas y motivarme para levantarme cada día, aunque no tuviera la energía para hacerlo.

Jorge Alfredo Bravo Lino

#### **DEDICATORIA**

A mi familia que en todo momento estuvieron ahí para brindarme su apoyo y a cada uno de mis amigos que confiaron en mí.

Edgar Javier Castillo Quinto

A mi madre deseo que siempre me apoyo, por lo que deseo se sienta orgullosa de mí, al igual que mi padre. También al resto de mi familia y amigos que confiaron en mí y que alguna vez dieron su granito de arena para que yo pudiera cumplir esta meta.

Jorge Alfredo Bravo Lino

### **DECLARACIÓN EXPRESA**

"La responsabilidad y la autoría del contenido de este Trabajo de Titulación, nos corresponde exclusivamente; Edgar Castillo y Jorge Bravo otorgamos nuestro consentimiento para que la ESPOL realice la comunicación pública de la obra por cualquier medio con el fin de promover la consulta, difusión y uso público de la producción intelectual"

Edgar Javier Castillo Quinto

Jorge Alfredo Bravo Lino

RESUMEN

Los sistemas industriales de medición de parámetros y control de procesos han

utilizado PLCs durante muchos años. Sin embargo, con el desarrollo de nuevas

tecnologías, su integración con nuevos fabricantes resulta compleja, lo cual incrementa

el costo de ingeniería.

La empresa ECRobotics ha desarrollado un sistema de medición de concentración de

nitritos en el agua que utiliza un PLC como sistema de control, y, el presente trabajo

presenta una propuesta para cambiar el controlador del sistema de medición por una

tarjeta de desarrollo con características más flexibles que permita escalar sus

funcionalidades.

Para efectuar el cambio del controlador, se estudiaron los detalles de la arquitectura

del dispositivo y se realizó una evaluación para la elección de una tarjeta de desarrollo

(FPGA) que cumpla con estos requerimientos. Para el control de los actuadores del

dispositivo, se desarrolló una tarjeta electrónica de comunicación. Además, un

programa embebido fue diseñado e implementado para el control del dispositivo de

medición y los actuadores.

Finalmente, se realizaron pruebas de comunicación entre la tarjeta de desarrollo y la

tarjeta electrónica, y, se ajustaron parámetros de calibración para garantizar el correcto

funcionamiento del dispositivo.

Palabras Clave: Controlador, componentes, escalabilidad, FPGA, concentración de

nitritos.

١

#### **ABSTRACT**

Industrial systems of parameters measurement and control process have used PLCs for many years. However, with the development of new technologies, its integration with new manufacturers results as a complex process. This makes the engineering work more expensive. The ECRobotics enterprise has developed a measurement system of nitrites concentration in water that uses a PLC in it.

This work shows a proposal to change the controller of the measurement device by an electronic development board with more flexible characteristics that make its functionalities escalate.

To make the controller change come true, the details of the architecture of the device were studied. An evaluation was done to choose a development board (FPGA) that accomplishes all the requirements. For the control of the device actuators, a communication electronic board was developed. What is more, an embedded program was designed and implemented for the control of the measurement device and its actuators.

Finally, a test of communication between the development board and the electronic board was done. Using those results, the calibration parameters were adjusted to secure the correct performance of the device.

Keywords: Controller, components, device, development board, FPGA, electronic card, measurement system

# ÍNDICE

| DEDICATORIA                                               | 4    |

|-----------------------------------------------------------|------|

| RESUMEN                                                   | I    |

| ABSTRACT                                                  |      |

| ABREVIATURAS                                              | V    |

| SIMBOLOGÍA                                                | VII  |

| ÍNDICE DE FIGURAS                                         | VIII |

| ÍNDICE DE TABLAS                                          | X    |

| CAPÍTULO 1                                                | 1    |

| 1. INTRODUCCIÓN                                           | 1    |

| 1.1 Descripción del Problema                              | 1    |

| 1.2 Justificación del Problema                            | 2    |

| 1.2.1 Justificación Técnica                               | 2    |

| 1.2.2 Justificación Económica                             | 3    |

| 1.2.3 Justificación Financiera                            | 4    |

| 1.3 Objetivos                                             | 4    |

| 1.3.1 Objetivo general                                    | 4    |

| 1.3.2 Objetivos Específicos                               | 4    |

| 1.4 Estado del Arte                                       | 5    |

| 1.5 Alcance                                               | 6    |

| 1.6 Metodología                                           | 7    |

| CAPÍTULO 2                                                | 9    |

| 2. MARCO TEÓRICO                                          | 9    |

| 2.1 Tarjeta lógica programable FPGA                       | 9    |

| 2.2 Características de una FPGA                           | 9    |

| 2.2.1 Arquitectura Programable                            | 9    |

| 2.2.2 Desarrollo acelerado                                | 9    |

| 2.2.3 Bajo costo de operación                             | 9    |

| 2.2.4 Integración de hardware                             | 10   |

| 2.3 Aplicaciones                                          | 10   |

| 2.3.1 Sistema de inteligencia artificial                  | 10   |

| 2.3.2 Radio definido por software                         | 10   |

| 2.3.3 Seguridad                                           | 11   |

| 2.5. Módulo de expansión de E/S digitales MicroLogix 1100 | 15   |

| CAPÍTULO 3                                                | 20   |

| 3. DI         | SEÑO DE LA SOLUCIÓN                                                                                | 20                    |

|---------------|----------------------------------------------------------------------------------------------------|-----------------------|

| 3.1.          | Funcionamiento del dispositivo de medición de NO <sub>2</sub>                                      | 20                    |

| 3.2.          | Proceso de medición de nitritos                                                                    | 22                    |

| 3.3.          | Esquema de interfaces electrónicas                                                                 | 24                    |

| 3.4.<br>el FF | Diseño del sistema digital programado en Quartus para la i<br>PGA y el sistema operativo del mismo |                       |

| 3.4           | .1. Bloque Generador de PWM                                                                        | 32                    |

| 3.4           | .2. Instanciación HPS                                                                              | 34                    |

| 3.4           | .3. Sistema Digital Completo                                                                       | 37                    |

| 3.5.          | Diseño del software controlador                                                                    | 39                    |

| 3.6.          | Análisis de Datos                                                                                  | 42                    |

| CAPÍT         | JLO 4                                                                                              | 43                    |

| 4. AN         | IÁLISIS DE RESULTADOS                                                                              | 43                    |

| 4.1.<br>defin | IMPLEMENTACIÓN DE INTERFACES ELECTRÓNICAS                                                          | ¡Error! Marcador no   |

| 4.2.          | IMPLEMENTACIÓN DEL ALGORITMO DE CONTROL. ¡Error!                                                   | Marcador no definido. |

| 4.3.          | ANÁLISIS DE COSTOS                                                                                 | 47                    |

| 4.4.          | Prueba de precisión                                                                                | 48                    |

| CONC          | _USIONES                                                                                           | 51                    |

| RECO          | MENDACIONES                                                                                        | 53                    |

| BIRL IC       | IGRAFÍA                                                                                            | 54                    |

#### **ABREVIATURAS**

ACP Accelerator Coherency Port

ADC Analog to digital converter

ASIC Application specific Integrated circuit

CADS Centro de Aguas de la ESPOL

CCU Cache Coherency Unit

CLBs Configurable logic blocks

CPU Unidad central de procesamiento

CVR Centro de Visión y Robótica

DAC Digital to analog converter

DDR Double Data Rate

DSP Digital Signal Processing

ECC Error Correction Code

ESPOL Escuela Superior Politécnica del Litoral

FPGA Field Programmable gate array

GPIO General Purpose Input Output

HDL Hardware Description Language

HMI Human Machine Interface

**HPS** Hard Processor System

I/O Input/Output

12C Inter integrated circuits

JTAG Join Test Action Group

LE Logic Elements

MPU Microprocessor Unit Subsystem

NAND Not AND

NO<sub>2</sub> Nitrito

OS Operative System

PCB Printed Circuit Board

PIO Parallel Input Output

PLC Controlador lógico Programable

PS Power Source

PWM Pulse Width Modulation

RS232 Recommended Standard 232

RTL Register Transfer Level

SD/MMC Secure Digital/ Multimedia Card Controller

SDRAM Synchronous Dynamic Random-Access Memory

SoC System on a Chip

SoCEDS System on Chip Embedded Development Suite

SOPC System on Programmable Chip

SPI Serial Peripheral Interface

TLB Translation lookaside buffer

UART Universal Asynchronous Receiver-Transmitter

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

## **SIMBOLOGÍA**

A Amperio

AC Analog Current

Cx Capacitor x

DC Direct Current

Dx Diode x

GB GigaBytes

mA Miliamperio

min minutos

mL mililitro

mV Milivoltio

mW miliWatts

nm nanometro

NO2 nitrito

P Potencia

Rx Resistencia x

Uf microFaradio

V Voltio

Vin Voltaje de entrada

Vout Voltaje de Salida

W Watt

β Direct Current Gain

# **ÍNDICE DE FIGURAS**

| Figura 2.1 PLCs Compactos Festo FEC FC660, Siemens Logo y S7-200               | . 13 |

|--------------------------------------------------------------------------------|------|

| Figura 2.2 PLC XBM-H Modular                                                   | . 13 |

| Figura 2.3 PLC's de montaje en rack: Siemens S7-400 PLC y Festo CPX PLC        | . 14 |

| Figura 2.4 OPLC Unitronics M-90                                                | . 15 |

| Figura 2.5 Módulo de expansión MicroLogix 1762                                 | . 15 |

| Figura 2.6 Bomba Peristáltica Gikfun 12V DC                                    | . 16 |

| Figura 2.7 Proceso de captación del líquido de la bomba peristáltica           | . 16 |

| Figura 2.8 Espectrofotómetro UV-Visible DR 3900                                | . 17 |

| Figura 2.9 Colorímetro CR-410                                                  | . 17 |

| Figura 2.10 Electroválvula AOMAG 1/4inch DC 12V                                | . 18 |

| Figura 2.11 Logo de inicialización del software                                | . 19 |

| Figura 2.12 Ventana principal del software Quartus Prime                       | . 19 |

| Figura 3.1 Diagrama de flujo del proceso de diseño                             | . 20 |

| Figura 3.2 Diagrama de bloques de la arquitectura del sistema                  | . 21 |

| Figura 3.3 Sensor de nivel Taidacent NPN                                       | . 22 |

| Figura 3.4 Diagrama de flujo del proceso                                       | . 24 |

| Figura 3.5 Integrado LM317 - Regulador de Voltaje                              | . 25 |

| Figura 3.6 Aplicación estándar para el LM317                                   | . 25 |

| Figura 3.7 Esquema de fuente regulada de 12V a 3V y 5V                         | . 26 |

| Figura 3.8 Diagrama de pines - Regulador LM7805                                | . 26 |

| Figura 3.9 Transistor TIP31                                                    | . 27 |

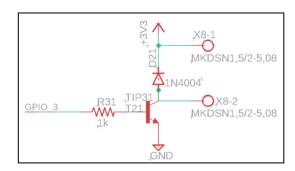

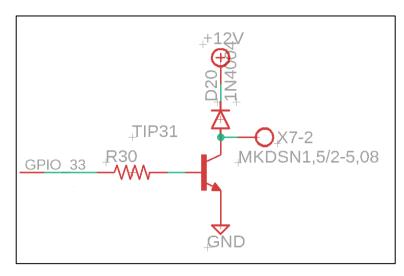

| Figura 3.10 Esquema electrónico para el control de un agitador                 | . 28 |

| Figura 3.11 Esquema electrónico de conexión de la Electroválvula               | . 29 |

| Figura 3.12 Esquema electrónico para el control de una Bomba peristáltica      | . 29 |

| Figura 3.13 Esquema completo para el manejo de periféricos en EAGLE            | . 31 |

| Figura 3.14 Diagrama de Bloques del sistema controlador                        | . 32 |

| Figura 3.15 Diagrama de entradas y salidas del bloque generador de PWM. Izquie | rda  |

| entradas y Derecha salidas                                                     | . 34 |

| Figura 3.16 Resumen del Sistema Qsys del controlador                           | . 34 |

| Figura 3 17 Diferencias entre Hard Processors usados en SOC FPGA's [15]        | 35   |

| Figura 3.18 Recursos utilizados por el sistema digital diseñado                         |

|-----------------------------------------------------------------------------------------|

| Figura 3.19 Compilación del Sistema Digital para la tarjeta de desarrollo DE0-nano      |

| SOC                                                                                     |

| Figura 3.20 Mapa de registros de un PIO (Parallel Input/Output)                         |

| Figura 3.21 Linealización de los datos para obtener una ecuación que los represente     |

| 4²                                                                                      |

| Figura 4.1 Diseño electrónico de placa en PCB utilizando Eagle                          |

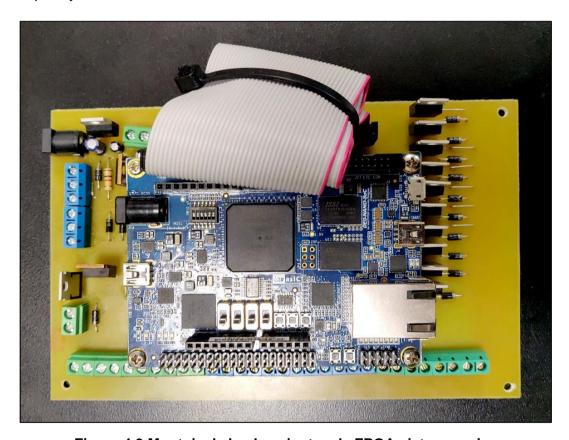

| Figura 4.2 Resultado final del montaje del circuito electrónico en PCB 44               |

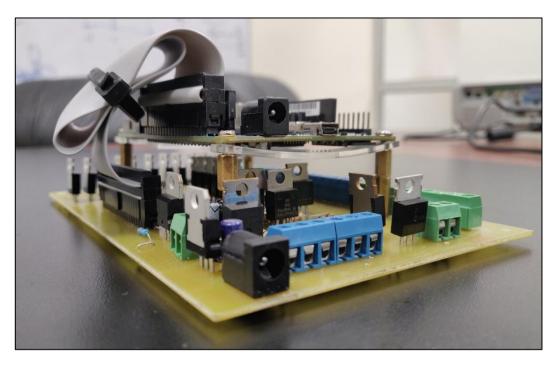

| Figura 4.3 Montaje de la placa junto a la FPGA vista superior                           |

| Figura 4.4 Montaje de la placa junto a la FPGA vista lateral                            |

| Figura 4.5 Salida de monitoreo del programa para el control del dispositivo de medición |

| de nitritos47                                                                           |

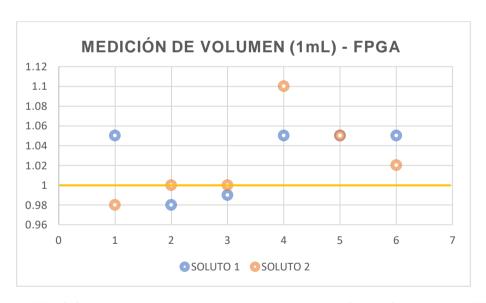

| Figura 4.6 Mediciones de soluto 1 y 2 tomando como referencia 1mL con FPGA 49           |

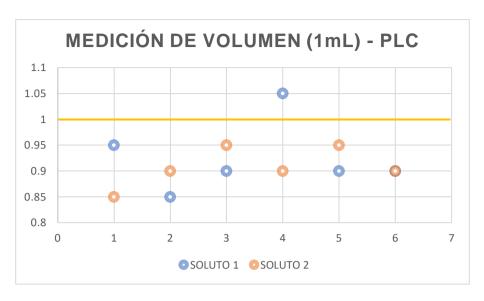

| Figura 4.7 Mediciones de soluto 1 y 2 tomando como referencia 1mL con PLC 50            |

# **ÍNDICE DE TABLAS**

| Tabla 3.1 Comparación de transistores 2n222 y TIP31                        | 28 |

|----------------------------------------------------------------------------|----|

| Tabla 3.2 Comparación entre FPGAs de bajo precio                           | 38 |

| Tabla 3.3 Configuración de puerta serial de la FPGA                        | 40 |

| Tabla 4.1 Gasto total de controlador para dispositivo de medición con FPGA | 48 |

| Tabla 4.2 Gasto total de controlador para dispositivo de medición con PLC  | 48 |

# **CAPÍTULO 1**

### 1. INTRODUCCIÓN

#### 1.1 Descripción del Problema

Desde la llegada de los PLC al mundo de la ingeniería estos han sido usados como una parte principal en la automatización de procesos ya sean industriales o de algún dispositivo que lo requiera [1]. La ventaja de éstos, es que son especializados para actividades de control; por lo que, todas las rutinas y protocolos de comunicación están desarrollados con el fin de cumplir dicha actividad [2]. Aunque también presentan algunas restricciones que dependen del fabricante, modelo y precio; por lo que, el PLC adecuado se elige de acuerdo con el tipo de proceso que se vaya a realizar; algunas de estas restricciones son el número o tipo de entradas, salidas, protocolos y capacidad de memoria para el programa. Además, los PLCs tienen licencias propietarias para el uso de software para la programación del PLC [3].

El PLC como dispositivo de control está siendo usado en el desarrollo de un dispositivo experimental para medir la concentración de nitritos presente en una muestra de agua. El desarrollo de este dispositivo está a cargo del Centro de Agua de la ESPOL (CADS) en conjunto con el Centro de Visión y Robótica (CVR). Dicho PLC controla la recolección de una muestra de agua desde el río mediante bombas peristálticas; luego, mezcla el agua con reactivos químicos dentro del dispositivo, y, finalmente un colorímetro, el cual no es controlado por el PLC, mide el nivel de luz que la muestra absorbe o refleja.

Con la finalidad de mejorar el producto, los Centros de Investigación mencionados anteriormente contactaron a ECRobotics, una empresa cuyo objetivo es crear sistemas de procesamiento de datos in-situ que puedan ejecutar algoritmos complejos basados en inteligencia artificial. Alinearse con este objetivo y mejorar el dispositivo son cosas difíciles de lograr con el PLC como sistema controlador, ya que, posee un lenguaje de programación de bajo nivel, como diagramas de escalera o de bloques, y el uso de estos depende del tipo de aplicación que se le dará, y, siendo de bajo nivel su uso se limita a realizar las tareas básicas, por lo que, se vuelve complejo el desarrollo de algoritmos

complejos y adaptativos que permitan tener una mayor versatilidad al momento de dar una solución a un problema. El PLC también se ve limitado al poseer diferentes entornos de programación dependiendo de la marca que se esté usando y el costo elevado de las licencias que se tienen que pagar anualmente por el servicio que brindan. En la práctica, un sistema basado en PLC puede requerir de equipos adicionales para poder tener capacidades de adquisición, procesamiento y transmisión de datos, lo cual incrementa su costo aún más.

Otra problemática del PLC es el uso de protocolos de comunicación entre dispositivos, que pueden o no ser inalámbricos, ya que muchos de estos protocolos o dispositivos que permiten establecer comunicaciones son propietarios, es decir, no son interoperables para diferentes marcas limitando el crecimiento y escalabilidad de algún sistema. En cambio, la FPGA puede usar una amplia gama de sensores, actuadores, y antenas que están disponibles a un menor costo y que pueden ser integradas aún si son de diferentes marcas, esto permite implementar comunicaciones inalámbricas fácilmente, ya que, en algunos casos se cuenta con soporte del fabricante y los aportes de la comunidad [3].

### 1.2 Justificación del Problema

#### 1.2.1 Justificación Técnica

Los PLC son sistemas basados en controladores que pueden ser usado para activar sensores, actuadores y ejecutar rutinas de control. Los PLCs modernos pueden realizar tareas de controles de forma simultánea y pueden ejecutar sus rutinas a altas frecuencias, pero no pueden realizar algoritmos complejos y adaptativos [4]. En cambio, el FPGA al ser una tarjeta lógica programable puede implementar de forma programada diferentes componentes de hardware que procesan señales digitales o análogicas, y que a diferencia del PLC es muy flexible; dado que, permite crear diferentes dispositivos como CPU, controladores, interfaces en una sola tarjeta.

Un FPGA con un sistema digital y un CPU que ejecuta un sistema operativo es conocido como un "System on a Chip" (SoC), refiriéndose a que en una sola tarjeta de desarrollo se encuentran integrados gran parte de los elementos que componen un computador. El SoC que ECRobotics propone puede ser usado

para realizar procesamiento inteligente de datos, y, presenta varias ventajas para el desarrollo de este proyecto.

Primero, Al tener un sistema operativo integrado, existe la facilidad de usar un lenguaje de programación de alto nivel, el cual, puede controlar elementos de hardware con tiempos de respuestas pequeños. Además, permite ejecutar varias tareas de forma paralela, ya que, el sistema operativo dentro del FPGA es multitarea. Así, el control o lectura de los elementos que componen el sistema de medición puede ser realizado desde algún programa que funcione como un proceso dentro del sistema operativo, y, a su vez, en una tarea paralela se puede analizar los datos que el colorímetro envía a través de una interfaz de programación (API) que el fabricante del dispositivo provee.

Segundo, se pueden combinar diferentes tipos de sensores, ya que el FPGA puede actualizar los componentes de control o captura de datos si el proceso de preparación de la muestra cambia. Por ejemplo, si se requieren mezclar más reactivos, se deberán agregar más actuadores o sensores, lo que implica el uso de una mayor cantidad de entradas/salidas del controlador, lo cual no será un problema para el FPGA, puesto que, este cuenta con una gran cantidad de GPIO (Pins de entrada y salida de propósito general) y varias interfaces de comunicación como I2C, SPI, entre otras. En cambio, para el PCL se deberá adquirir módulos de expansión de entradas/salidas e incluso en algunos casos adquirir un controlador diferente, no será necesario adquirir otro equipo de control, a diferencia de usar PLCs, lo cual si ocurre. Simplemente se pueden agregar más bloques de control o cambiar su programación en el FPGA [5]. Además, con la investigación necesaria se puede agregar sensores diferentes que permitan mejorar el proceso de estimación de la concentración de nitritos e incluso que permitan derivar otros parámetros de interés de manera indirecta.

Finalmente, al ser un dispositivo programable el uso de FPGA D0 Nano reduce los tiempos de adaptación de nuevas tecnologías y su precio de mercado ronda los 130USD para la escala del problema que se espera resolver [6].

#### 1.2.2 Justificación Económica

Hoy en día el mercado ofrece una amplia gama de dispositivos de control que se adaptan a las necesidades del usuario. Entre ellas tenemos el PLC micrologix 1100 con un valor en el mercado de \$348.90 y una FPGA D0 Nano SoC a \$130 dólares, evidentemente la diferencia de precios es notable. Además, el PLC nombrado tiene otro punto en contra, la falta de entradas o salidas digitales, lo cual puede solucionarse con un módulo de expansión, pero, el costo final del controlador incrementa considerablemente, esto lo diferencia del FPGA ya que este cuenta con aproximadamente 80 entradas/salidas sin necesidad de módulos adicionales [5].

#### 1.2.3 Justificación Financiera

El proyecto cuenta con el respaldo del cliente ECRobotics, propietario del dispositivo experimental, ya que brinda las herramientas y materiales necesarios para el diseño del prototipo de sistema controlador basado en FPGA. El beneficio que obtiene nuestro cliente es poder extender la funcionalidad de su plataforma sin tener que comunicarse con un PLC externo. Esto se traduce en menores costos de producción y un dispositivo de calidad capaz de cumplir con los requerimientos del cliente. Además, que con el reacondicionamiento del dispositivo experimental se puede incrementar la productividad y eficiencia de la maquinaria que maneja en su interior.

### 1.3 Objetivos

#### 1.3.1 Objetivo general

Diseñar y construir un prototipo basado en FPGA y sistemas embebidos, capaz de controlar dispositivo de medición e identificación de niveles de NO2 en cuerpos de agua.

#### 1.3.2 Objetivos Específicos

- Conocer la arquitectura, funcionamiento y parámetros necesarios que el dispositivo de medición de NO2 usa actualmente, para establecer los requerimientos del nuevo controlador.

- Realizar un diagrama de flujo con el proceso completo que el dispositivo experimental de medición de nitritos realiza, para la identificación de nitritos; como ayuda para la realización del programa.

- Diseñar interfaces electrónicas para la interconexión de los elementos de potencia con las entradas/salidas digitales o analógicas de la FPGA.

- Diseñar componentes de software que sirvan como drivers para la interconexión de los elementos eléctricos o electrónicos, que usa el dispositivo de medición de NO2.

- Implementar el sistema controlador para evaluar los resultados y realizar ajustes de calibración que permitan su correcta operación.

#### 1.4 Estado del Arte

Basado en los trabajos previos realizados en el mismo campo, pero con aplicaciones diferentes, podemos conocer información útil previa a la realización del proyecto.

Los diferentes estudios se basan en si en la implementación de sistemas en FPGA orientadas a diferentes requerimientos los cuales se van a presentar en orden cronológico, esto permite conocer las mejoras realizadas a las tecnologías existentes que se han ido desarrollando en el tiempo. Por lo cual, a través de este análisis se puede identificar el precedente de lo que se espera lograr en el proyecto presente y futuros similares.

La necesidad de tener un controlador con más capacidad de procesamiento ha llevado a la industria del moldeo por inyección a buscar alternativas que puedan cumplir con la demanda de todos los procesos que se requieren para llevar a cabo la realización del producto final, como lo propone el siguiente artículo "Controlador modular y reconfigurable para máquina de inyección de plástico basado en FPGA". El moldeo por inyección de plástico es un proceso que maneja variables como: velocidad, presión, temperatura, posición y otros eventos discretos que requieren de una capacidad de cómputo muy superior a la que ofrece un PLC, el cual tiene una limitante en su arquitectura, condicionando el desempeño del proceso. La solución fue usar un dispositivo dispositivo de alto desempeño como la FPGA, en la cual se diseñó un sistema modular que maneje todos los procesos involucrados; y, se añadió un módulo de comunicación. Las pruebas del sistema se hicieron en una máquina de inyección Husky, dando como resultado un sistema que controle el sistema de inyección de forma eficiente, lo que convierte al FPGA en una opción viable para empresas

pequeñas y medianas que necesitan incrementar el nivel de productividad de su maquinaria [7].

En el siguiente proyecto "Implementación de un FPGA para control y adquisición de datos mediante una unidad de telemetría remota" se decidió como parte de un proyecto de renovación de equipos, usar como controlador un FPGA con la finalidad de mitigar la carga de procesamiento de datos y la necesidad de adicionar un sistema de comunicación. Con esto lograron obtener un sistema de chip programable que satisfaga todas sus necesidades y con la capacidad de conectarse a internet. Como resultado se obtuvo un dispositivo compacto, bajo costo y de alta velocidad de procesamiento [2].

Además "Implementación en dispositivos FPGA de controladores para sistemas lineales inestables con retardo de tiempo", el cual usa el FPGA para compensar los retardos y lograr más estabilidad en el sistema, cuando este actúa en lazo cerrado. El resultado obtenido fue un "control" estable gracias a la predicción de la salida del sistema, y, gracias a la capacidad de procesamiento de la FPGA, se puede incluir un modelo "Real" para la realización de pruebas en tiempo real, sin necesidad de contar con el sistema físico sino más bien emulado[8].

Al revisar los trabajos relacionados se nota que básicamente se ha usado al FPGA como tarjeta de desarrollo y controlador de dispositivos digitales que no manejan potencia, y en uno que otro caso tratan de emular un PLC, nuestro proyecto se diferencia, ya que no solo se reemplazará al PLC, sino, que se harán las interfaces necesarias para que este maneje los elementos de potencia y además combinar el sistema embebido de la FPGA para desarrollar algoritmos más complejos que realice de forma automática el análisis de los datos obtenidos del sistema de medición.

#### 1.5 Alcance

El proyecto incluye la realización de las interfaces electrónicas de conexión entre los dispositivos de potencia (motores, bombas peristálticas, etc.) usados dentro del sensor experimental y la FPGA.

Se incluye también la realización de los módulos o programas en la FPGA para el control de los dispositivos mencionados anteriormente incluyendo sus protocolos de comunicación y el programa completo que maneje el sensor experimental y todas las etapas necesarias para obtener las mediciones.

Incluye la realización de un algoritmo de análisis de los datos obtenidos, manejado desde el Sistema Operativo de la FPGA y además una salida serial para el monitoreo del proceso de medición.

Este proyecto no incluye la integración con la red SCADA, ya que se pretende únicamente darle más capacidades al dispositivo de medición y hacerlo más "inteligente", de tal forma que pueda ser usado en futuro por la plataforma de ECRobotics, la empresa contratante

#### 1.6 Metodología

El proyecto se dividirá en varias etapas, de las cuales, la etapa inicial será conocer el funcionamiento de cada uno de los elementos que conforman el sistema de medición del dispositivo experimental. En esta etapa se deberá conocer cómo dichos elementos se involucran en el proceso de medición de la concentración de nitritos, para luego poder conocer correctamente el proceso que el dispositivo realiza.

Con el conocimiento de los elementos que conforman al sistema, se estudia el proceso que el PLC realiza para las mediciones, con el objetivo de obtener un diagrama de flujo que describa dicho proceso, lo que luego facilitará la implementación del mismo en un lenguaje de programación de alto nivel dentro del sistema embebido de la FPGA.

De acuerdo con el diagrama de flujo se realizará una estimación de la capacidad de procesamiento necesaria para realizar todo el proceso, y con esta se definirá el FPGA requerido.

Luego se realizarán las adecuaciones eléctricas y/o electrónicas necesarias para cada sensor o actuador, de tal forma que estos puedan ser manejados por los niveles de voltaje y corriente con los que opera el FPGA.

Conociendo el cómo se conectarán los elementos de control a la FPGA se deberá implementar un circuito digital programado haciendo uso del VHDL que servirá como interfaz (Driver) entre estos elementos y el sistema operativo instalado en la FPGA.

Con el diseño de control completo y su implementación se construirá un algoritmo capaz de analizar los resultados y dar conclusiones acerca de los datos obtenidos.

# **CAPÍTULO 2**

#### 2. MARCO TEÓRICO

#### 2.1 Tarjeta lógica programable FPGA

Por sus siglas en ingles es Field Programmable Gate Array o en español Arreglo de Compuertas Programables en Campo. La FPGA es una tarjeta lógica programable que posee subcircuitos digitales programables y configurados para una amplia gama de aplicaciones, es decir, que internamente se configura para que sea un dispositivo con una tarea específica y que luego puede ser reconfigurado. La capacidad de ser reprogramable lo hace un dispositivo con capacidades ilimitadas, permitiendo realizar diseños digitales eficientes y a la medida del proyecto que se desea realizar [9].

El FPGA puede ser programado mediante dos tipos de lenguaje populares como lo son VHDL y Verilog. El tipo de programación usado no es el tradicional en donde se introducen instrucciones, sino que se "programa" la descripción del hardware, es decir se realiza el diseño de la arquitectura a nivel de hardware [10].

#### 2.2 Características de una FPGA

#### 2.2.1 Arquitectura Programable

Poseer una arquitectura programable significa que podemos optimizar los procesos que realizara la tarjeta y realizar cambios para mejorar el rendimiento. El lenguaje de programación de bajo nivel como VHDL describirá la forma en cómo será usado el hardware [11].

#### 2.2.2 Desarrollo acelerado

Los FPGA en su interior posee diminutos semiconductores basados en matriz de bloques configurables o CLBs, es decir trabajan a nivel lógico. Esto permite que se puedan traer versiones con mayor capacidad de procesamiento en menos tiempo que la competencia, ya que requiere de ciclos de fabricación más extensos [11].

#### 2.2.3 Bajo costo de operación

Los dispositivos ASIC que son circuitos integrados dedicados a aplicaciones específicas, pueden llegar a ser más económicos que una FPGA, pero poseen

un hardware estático y no se pueden realizar cambios a futuro, esto lo diferencia de una FPGA, ya que, este puede realizar mejoras en su arquitectura fácilmente, cambiando simplemente la programación de su descripción de hardware. Un ejemplo muy claro es cuando tenemos un dispositivo ASIC funcionando y se requiere de una actualización del sistema, esto hace que el ASIC deba ser reemplazado por uno más actualizado o mejor que maneje las nuevas configuraciones; pero, con un FPGA no hay necesidad de cambiar el dispositivo, sino realizar la reconfiguración de su hardware de tal forma que se acople a las nuevas necesidades del sistema [11].

#### 2.2.4 Integración de hardware

Los FPGA poseen sistemas de entrada y salida, procesadores y muchas funciones más. Esto significa que requiere de menos dispositivos externos para llevar a cabo más funciones. A diferencia de los dispositivos ASIC que tienen en su interior chips conectados en paralelo, es decir si uno de ellos falla significa que todo el dispositivo fallara [11].

#### 2.3 Aplicaciones

Debido a la versatilidad y flexibilidad del FPGA, el abanico de aplicaciones es muy amplio. Su principal aplicación está orientada al procesamiento digital de señales (DSP), circuitos digitales, procesamiento de datos y comunicaciones [12].

#### 2.3.1 Sistema de inteligencia artificial

Hoy en día cada vez son más los dispositivos que poseen un sistema de visión artificial como robots, cámaras de vigilancia, celulares, etc. Estos dispositivos necesitan reconocer objetos, reconocer rostros e incluso conocer distancias para conocer su posición e interactuar mejor con el entorno. El análisis de un alto volúmenes de imágenes requiere de una capacidad de procesamiento elevado y además deben ser procesadas en tiempo real [12].

#### 2.3.2 Radio definido por software

Un radio está compuesto por una antena que se encarga de enviar y recibir la señal y un hardware que procesa la señal. Este hardware era dedicado y modular, es decir, existía un hardware específico para cada función de un sistema de telecomunicaciones. Hoy en día ya no se usan chips dedicados a aplicaciones específicas, sino más bien se usa un procesador de propósitos generales y dentro de este se programan todos los componentes necesarios para el sistema de comunicaciones, esto es conocido como SDR (Radio Definido por Software). Algunos FPGA cuentan con sistemas ADC y DAC integrados, y, en conjunto con su capacidad de reconfiguración de hardware, los hace un dispositivo perfecto para un sistema de Radio Definido por Software [12].

#### 2.3.3 Seguridad

El envió de información de forma segura es primordial, ya que, realizar procedimientos como una compra online o realizar una transferencia bancaria sin una seguridad adecuada en los datos transferidos, puede suponer una gran pérdida de recursos, por esto, la capacidad de un FPGA de manejar un gran volumen de datos y bloques optimizados para realizar opciones aritméticas que permiten la encriptación eficiente al enviar información es una gran opción para aplicaciones de seguridad informática [12].

#### 2.4 Controlador Lógico Programable PLC

Un PLC o Programmable Logic Sistem por sus siglas en ingles. Es un dispositivo dedicado a realizar procesos electromecánicos en el área de automatización industrial. Procesos como el control de maquinaria en líneas de montaje hasta el control de iluminarias son unas de las muchas aplicaciones que son capaces de realizar [13].

Los PLC son capaces de llevar a cabo varios procesos a la vez, entre sus características tenemos que poseen múltiples entradas y salidas, resistencia a la vibración, rango alto de temperatura, inmunidad al ruido eléctrico y resistentes a impactos. Ideal para procesos con condiciones ambientales que requieran de un dispositivo resistente [13].

El PLC es un dispositivo que tiene la capacidad de conexión directa, es decir que puede ser conectado a valores de tensión y corriente de niveles industriales.

#### 2.4.1 Ventajas y desventajas del uso de un PLC

#### **Ventajas**

- Facilidad de programación por no especialistas.

- Capaz de comunicarse con otros PLCs y ordenadores.

- Ideal para uso industrial ya que soporta humedad, polvo, vibraciones, temperatura y ruido.

- Seguridad de control de procesos.

- Manejo de múltiples actuadores.

- Rápida detección de averías.

- Bajo costo de instalación, mantenimiento y operación.

#### Desventajas

- El costo inicial para autorizar un proceso es elevado, no es recomendado implementarse en tareas sencillas.

- Mano de obra con personal especializado.

- Para automatizar una tarea es necesario tener en cuenta todos los detalles al momento de programar.

#### 2.4.2 TIPOS DE PLC

#### **PLC COMPACTOS**

Los PLC compactos traen todo en un solo paquete, incluyen PS, CPU, módulo de entrada y salida de hasta 30 slots fijo, canales de comunicación para programar el PLC e interfaz hombre maquina (HMI). Algunos modelos incorporan una conexión de entrada de alta velocidad al controlador, dos entradas o salidas analógicas. En caso de tener la necesidad de aumentar el número de entradas o salidas es necesario adquirir un módulo. Normalmente usados como sustitutos de relés [13].

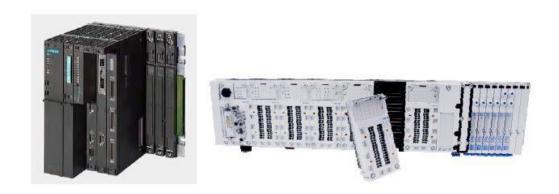

Figura 2.1.- PLCs Compactos Festo FEC FC660, Siemens Logo y S7-200

#### **PLC Modular**

Este tipo de PLC viene equipado con más funciones y mejores características en su hardware, que un PLC compacto. La SM, CP, CPU y accesorios adicionales que se pueden añadir por separado. Posee un número limitado de lugares en donde se pueden colocar módulos, pero en caso de llegar a necesitar más pueden aumentarse. Los PLC modulares integran una mayor cantidad de entradas y salidas, mayor capacidad de memoria maneja programas más robustos, lleva a cabo múltiples tareas. Usualmente se emplean para el procesamiento de datos, posicionamiento, monitoreo, comunicación y servicios web [13].

Figura 2.2.- PLC XBM-H Modular

#### PLC de montaje en RACK

Este tipo de PLC tienen la misma capacidad que un PLC modular, pero su principal diferencia está en el rack y bus de datos donde los módulos son colocados. Este PLC tiene ranuras para colocar módulos y un bus integrado para la comunicación entre módulos. Su principal ventaja es la capacidad de realizar un intercambio rápido de información de datos entre módulos lo que se traduce en un menor tiempo de respuesta a diferencia de otros módulos que solo disponen de un panel frontal con interfaz HIM [13].

Figura 2.3.- PLC's de montaje en rack: Siemens S7-400 PLC y Festo CPX PLC

#### PLC con panel operador

Estos PLC incluyen una interfaz HIM que facilitan el monitoreo y control de procesos y maquinas. Una interfaz HIM es una pantalla táctil si es un modelo actual o un monitor y teclado si es un modelo antiguo. Su principal ventaja es que al traer un panel operador aparte no es necesario programarlo por separado, sino que toda la programación se realiza por medio de una herramienta o software [13].

Figura 2.4.- OPLC Unitronics M-90

#### 2.5. Módulo de expansión de E/S digitales MicroLogix 1100

Mediante este módulo se pueden ampliar el número de E/S que serán necesarias para su proyecto. Este es un diseño modular sin rack que es más económico y reduce los costos por piezas de repuesto en caso de desperfecto.

- Modelo MicroLogix 1762

- Manejo de voltaje alterno (AC) y continuo (DC)

- Relé de DC/AC

- Disponible en 8, 16 o 32 E/S digitales

- Modulo combinado con 6 salidas de contacto y 8 entradas

Figura 2.5.- Módulo de expansión MicroLogix 1762

#### 2.6. Bomba peristáltica

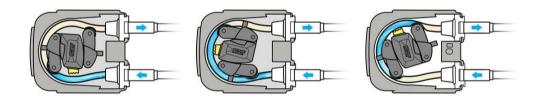

Una bomba peristáltica también conocida como bomba de desplazamiento positivo porque tiene una parte por donde succiona el fluido y otra por donde es expulsado. El líquido es transportado por un tubo flexible que está dentro de la cubierta circular, además tiene un rotor con unos rodillos los cuales al girar van a empujar el liquito por el tubo flexible.

Figura 2.6 Bomba Peristáltica Gikfun 12V DC

#### **Funcionamiento**

Los rodillos al interior de la cavidad circular al girar comprimen el tubo flexible que crea un vacío que succiona al fluido a través del tubo flexible. La ventaja de este tipo de bombas es que al ser comprimida la manguera se genera un flujo positivo del fluido evitando que se generen reflujos, de esta manera no es necesario el uso de valvulares reguladoras.

Figura 2.7.- Proceso de captación del líquido de la bomba peristáltica

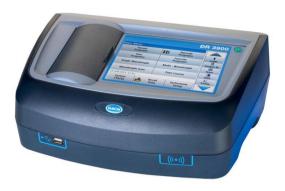

#### 2.7. Espectrofotómetro

Es un instrumento de análisis óptico que permite comparar el nivel de radiación absorbida por una muestra de solución que contiene una cantidad desconocida de soluto y una que tiene una cantidad conocida de ese soluto.

El espectrofotómetro proyecta un haz de luz monocromático sobre la muestra y mide la cantidad de luz absorbida sobre ella. Como resultado tenemos:

- Información de la naturaleza de la sustancia que posee la muestra

- Cantidad de sustancia presente en la muestra.

Figura 2.8.- Espectrofotómetro UV-Visible DR 3900

#### 2.8. Colorímetro

Es una herramienta que mide la absorbancia de una sustancia, ésta consiste en que la absorbancia es directamente proporcional a la concentración de la sustancia en estudio. El colorímetro mide la concentración de una sustancia a partir de la identificación de colores y sus diferentes variantes por ello si una sustancia tiene mayor concentración presentara mayor absorbancia.

Cada sustancia es capaz de absorber diferentes frecuencias que se traducen en colores. Para realizar las mediciones se usa un filtro que seleccionará el color de luz que será absorbido por el soluto, esto permite tener un mejor resultado en la medición de la muestra. Nótese que el color que más absorbe el soluto es el opuesto al color que presenta la muestra.

Figura 2.9.- Colorímetro CR-410

#### 2.9. Electroválvula

Una electroválvula funciona con un mecanismo electromecánico y está diseñada para permitir o impedir el paso de fluido. El mecanismo es accionado a través de una bobina

cuyo voltaje de accionamiento dependerá de las especificaciones del fabricante. Por lo general posee únicamente dos estados, abierto o cerrado y pueden ser usadas en un sin número de situaciones para el control de fluidos.

Figura 2.10.- Electroválvula AOMAG 1/4inch DC 12V

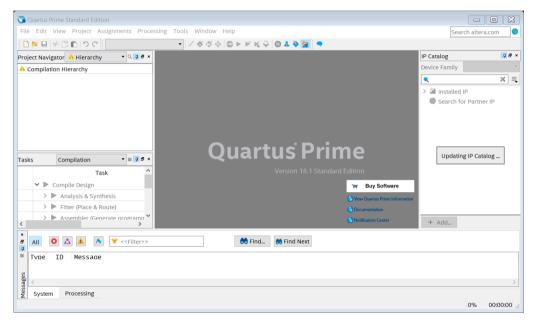

#### 2.10. Intel Quartus Altera

Es un programa de diseño para dispositivos lógicos programables que permite al usuario la síntesis de diseños HDL, análisis de diagramas RTL, realizar simulaciones de un diseño, configurar un dispositivo de acuerdo con el objetivo al que desea llegar el programador. Quartus posee un apartado prime que permite al usuario usar VHDL para la programación del hardware. Además, se puede realizar la edición de circuitos lógicos en una interfaz gráfica [14].

#### Características de Intel Quartus Prime:

- Incluye SOPC Builder, herramienta que elimina los procesos manuales al momento de generar la interconexión de una tarjeta lógica y verificar su funcionamiento mediante un banco de pruebas.

- DSP Builder, herramienta que permite a Quartus tener una conexión directa con Matlab y simulink.

- SoCEDS, herramienta que contiene ejemplos de aplicaciones que ayudan al desarrollador a crear nuevas herramientas.

- Qsys herramienta que permite la integración de sistemas, es una versión más avanzada que SOPC Builder.

Figura 2.11 Logo de inicialización del software

Figura 2.12 Ventana principal del software Quartus Prime

# **CAPÍTULO 3**

### 3. DISEÑO DE LA SOLUCIÓN

El proceso de diseño consiste en conocer la arquitectura, funcionamiento y características eléctricas del dispositivo de medición. Una vez que se tenga una idea detallada del proceso y como lo lleva a cabo el aparato. Se empezará por la elaboración de un diagrama de flujo del proceso de medición de nitritos, elección de los componentes necesarios para llevar a cabo el reemplazo del controlador. Seguido del diseño de las interfaces electrónicas que permitirán que el FPGA pueda manejar cada uno de los periféricos del dispositivo de medición sin ningún problema. También se lleva a cabo el diseño del software que permita la interacción y control de cada uno de los periféricos para luego realizar el montaje del FPGA y sus adaptaciones. Para finalizar se realizará pruebas de funcionamiento y calibración.

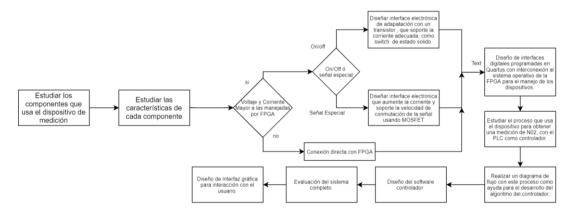

A continuación, en la Figura 3.1 se presenta un diagrama de flujo que detalla el proceso de diseño del sistema controlador basado en FPGA.

Figura 3.1 Diagrama de flujo del proceso de diseño

#### 3.1. Funcionamiento del dispositivo de medición de NO<sub>2</sub>

En este apartado se realiza el estudio del funcionamiento previo del dispositivo experimental de medición de NO<sub>2</sub>. Este dispositivo basa su funcionamiento en la colorimetría, es decir, internamente realiza reacciones químicas de ciertos compuestos con la muestra de agua; para que al final esta se torne de un color específico que represente la cantidad de nitrito presente en la muestra. La obtención de datos de esta mezcla "coloreada" se realiza a través de

espectrofotometría que analiza en base a longitudes de ondas el color de la muestra, y, con esto determina la concentración de NO<sub>2</sub> presente en la muestra.

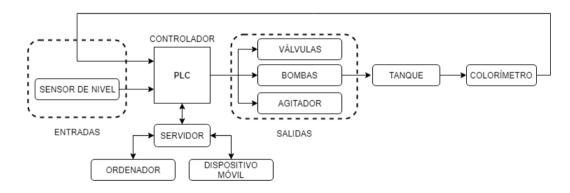

#### 3.1.1 Arquitectura

El dispositivo de medición posee un PLC que es el encargado de recoger la señales de cada uno de los sensores y accionar los actuadores en cada una de las etapas del proceso de medición de nitrito. El PLC cuenta con una conexión a un servidor que le permite guardar cada uno de los datos obtenidos, además cuenta con un ordenador enlazado al servidor que tiene una aplicación para el monitoreo de las mediciones hechas por el dispositivo. El esquema de la arquitectura de funcionamiento del dispositivo se muestra en la Figura 3.2 a continuación.

Figura 3.2.- Diagrama de bloques de la arquitectura del sistema

#### 3.1.2 Componentes del sistema

**PLC Micrologix 1100** funciona como controlador del sistema, cuenta con 10 entradas digitales, 6 salidas tipo relé y comunicación Ethernet. Se le puede añadir un módulo de expansión de 16 salidas digitales (1762 IQ16) y un módulo de 16 salidas tipo relé (1762 OW16).

Sensor de nivel IS NPN opera con un nivel de voltaje de entre 5 y 12V. Este sensor no necesita estar en contacto con el líquido para proporcionar las medidas. Es un sensor digital, es decir, se encarga de indicar si existe o no liquido presente en el nivel o altura del recipiente en el que se encuentre colocado. Si el nivel de la solución se encuentra bajo acciona una alarma para que el operador se acerque a llenar los recipientes.

Figura 3.3 Sensor de nivel Taidacent NPN

**Electroválvulas** son las encargadas de controlar el paso de líquidos a través de las mangueras. Posee dos vías normalmente cerradas con un diámetro externo de 6 mm en sus conectores.

**Bombas peristálticas** se encarga de desplazar los fluidos con un caudal contante por las mangueras. Las bombas de la marca Gikfun AE1207 manejan un caudal de entre 0 a 100mL/min, posee cañerías con diámetro interno de 3mm.

Mangueras, usa dos tipos de manguera una con un diámetro interno de 3 mm y diámetro externo de 4 mm, la segunda manguera tiene un diámetro interno de 2 mm y diámetro externo de 4 mm. Es importante recalcar que usa la maguera con menor diámetro para tener mayor control de la solución al momento de medirla, es decir si se necesita 0,5 mL de solución se requerirá que el fluido se encuentre en 159,14 mm de manguera con 2 mm de diámetro interno.

Recipientes color ámbar, el dispositivo usa este tipo de recipientes para proteger las soluciones (reactivos) de la presencia de luz, ya que son de características fotosensibles.

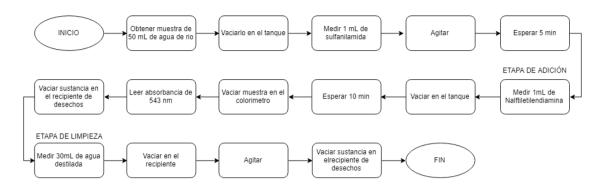

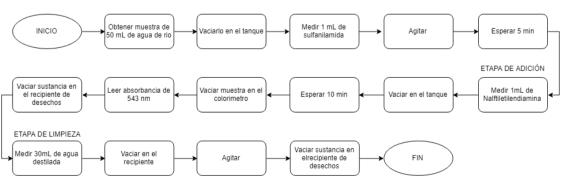

### 3.2. Proceso de medición de nitritos

El proceso se divide en cuatro etapas, reduciendo al máximo la intervención humana y obtener los resultados de concentración de nitritos en la muestra.

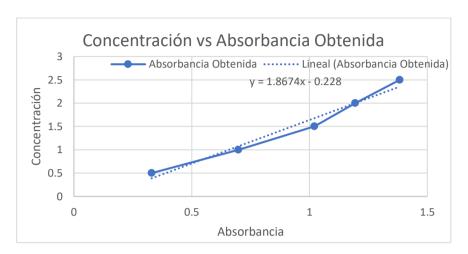

Etapa Cero: Calibración. El dispositivo realizar un proceso de calibración que permitirá obtener una representación gráfica de absorbancia y concentración de nitrito. Se mide 1ml de la solución patrón y 100ml de solución desionizada, se obtiene una mezcla con 1 umol/L de concentración. Se toma muestras de 0,25 0.50 0.75 1 y 1.25 mL, se completa con 25mL. Estas muestras son analizadas por el colorímetro que medirá el nivel de absorbancia de cada muestra. Mediante la técnica de regresión lineal se obtiene la gráfica que obedece a la ecuación 3.1, la cual representara la conversión entre absorbancia y concentración para mediciones futuras, con muestras de niveles de concentración desconodidas.

$$Y = mX + b \tag{3.1}$$

Donde Y representa el valor de absorbancia, X la concentración de la muestra y b el intercepto en el eje X.

**Etapa Uno,** denominada dosificación, realiza la medición del volumen de muestra y volumen de soluto necesario para cada mezcla con la ayuda de las bombas peristálticas y el control con las electroválvulas.

**Etapa Tres,** denominada medición, la muestra ya posee todos reactivos y después de entrar en reposo por un determinando tiempo será analizada por el colorímetro.

**Etapa Cuatro**, denominada limpieza, una vez realizada las mediciones correspondientes se procede a desechar la solución y verter agua destilada en los recipientes usado para mantener los recipientes libres de residuos que puedan contaminar las siguientes muestras y alterar los resultados de medición.

Figura 3.4 Diagrama de flujo del proceso

### 3.3. Esquema de interfaces electrónicas

La FPGA al ser una tarjeta programable tiene una entrada de alimentación de 5v y es capaz de generar voltaje de salida de 3.3v y 5v en sus salidas digitales. En cambio, los actuadores y elementos que serán usados en el sistema de medición trabajan con un nivel de 12 voltios y una corriente mayor a la que soporta el FPGA, por esa razón es necesario el diseño de una interfaz de acondicionamiento electrónico. El esquema maneja 14 electroválvulas, 5 bombas peristálticas, 1 agitador, 2 fuentes reguladas stepdown que permite manejar voltaje de 3v y 5v.

Cada circuito de control es asignado a cada salida GPIO que posee la FPGA, de esta forma todo estará integrado en un solo circuito que converge en un bus de datos.

### Diseño de fuentes reguladas

En la Figura 3.7 se presenta el esquema de dos fuentes step-down que reducen el nivel de tensión. Se decidió usar este tipo de fuente lineal porque es de fácil construcción, usa pocos elementos, eficaz, baratas y se adecúa a las necesidades del proyecto.

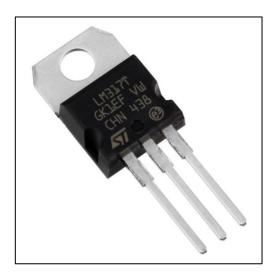

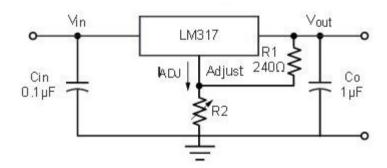

El LM317 es un regulador de voltaje ajustable con un rango de 1.25V a 37V en la salida e intensidad de 1.5A. Posee tres pines: ADJ, entrada y salida.

Figura 3.5 Integrado LM317 - Regulador de Voltaje

En el datasheet del LM317 el fabricante presenta un esquema de aplicación típica que ilustra la configuración de una fuente regulada.

Figura 3.6.- Aplicación estándar para el LM317

El voltaje de salida no depende de los condensadores que se encuentran tanto a la entrada como a la salida como se muestra en la Figura 3.6. El propósito de colocar C<sub>IN</sub> y C<sub>o</sub> es de mejorar la respuesta transitoria y mejorar el rechazo del rizado de la señal, obteniendo como resultado una señal más limpia y lineal posible.

El nivel de tensión de salida del regulador de voltaje de la Figura 3.6 puede ser calculado a partir de la ecuación 3.2, donde  $V_{Ref}$  tiene un valor de 1.25V y  $I_{ADJ}$  con 50uA. En la ecuación 3.3 se observa el cálculo de las resistencias R2 y R1 para lograr una salida de 3V a la salida.

$$V_o = V_{Ref} \left( 1 + \frac{R_2}{R_1} \right) + I_{ADJ} R_2 \tag{3.2}$$

$$V_o = 1.25 \left( 1 + \frac{330}{240} \right) + (50uA)(330) = 2.99V$$

(3.3)

En la parte superior de la Figura 3.7 se tiene una fuente de 12V a 3V y dada las características mencionadas anteriormente del LM317, en conjunto con la obtención de resistencias comerciales (resistencias de  $240 \ y \ 330$ ) la obtención de 3V a la salida de la fuente fue algo sencillo y económico.

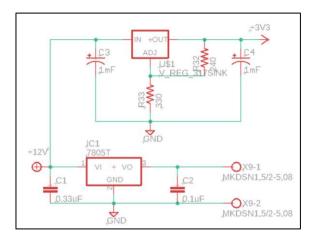

Figura 3.7 Esquema de fuente regulada de 12V a 3V y 5V

En la parte inferior de la Figura 3.7 se tiene una fuente regulada de tipo stepdown que va de 12V a 5V que será usada para la alimentación de la FPGA.

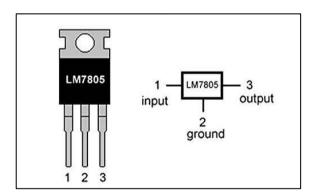

Figura 3.8.- Diagrama de pines - Regulador LM7805

Una solución para obtener un nivel de tensión de 5V es usar un regulador de voltaje LM7805 que posee una limitante en la tensión de entrada de hasta 35V. Otra limitante de este integrado es el calor que genera, si la diferencia de voltaje entre la entrada y la salida es demasiado grande, este no es un problema para el presente diseño, ya que en este se requiere un voltaje de entrada de 12V y un

voltaje de salida de 5V. En caso de tener una diferencia muy grande, se deberá usar un disipador de calor.

### Diseño de interfaz electrónica de un agitador

Dentro de los elementos que se necesitan controlar esta un agitador, el cual será el encargado de mezclar los líquidos que llegan al recipiente para formar una mezcla uniforme y coloreada que luego será analizada en el colorímetro. Esta interfaz debe ser capaz de funcionar a un voltaje de 3V y una corriente mínima de 400mA.

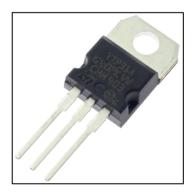

La mejor opción de acuerdo con los requerimientos del agitador fue usar un transistor TIP31 Figura 3.9 que es un transistor usado para conmutación en circuitos de potencia, y, es capaz de manejar corrientes de hasta 3A y soportar un voltaje en la juntura base-emisor de 100V. Estas especificaciones se adecuan a la aplicación que se le dará en el presente proyecto.

Figura 3.9.- Transistor TIP31

El circuito de la Figura 3.10 es el esquema para el control del agitador, su funcionamiento se basa en un switch de estado sólido, es decir cada vez que llegue la señal de voltaje en la base el transistor TIP31 se polarizara y entrara en zona de saturación permitiendo que el agitador se accione, caso contrario el transistor estará en zona de corte apagando el agitador. En el colector se tiene un diodo que hace de protector de corriente, impidiendo que corrientes inversas puedan dañar el agitador, el circuito o la FPGA.

Figura 3.10 Esquema electrónico para el control de un agitador

Para la selección del transistor empleado en circuito de la Figura 3.10 es necesario conocer la potencia que el agitador consumirá en condiciones de switcheo. Las variables necesarias para hacer el cálculo de potencia consumida por la carga es el voltaje colecto-emisor del transistor y la corriente mínima a la que opera la carga.

$$P_{switching} = V_{CE(Sat)}I_{MinCarga}$$

(3.3)

En la Tabla 3.1 se realiza la comparación de potencias consumida por la carga para cada transistor. En el caso del 2n222 la potencia consumida es de 0.64W que sobrepasa la potencia máxima de 0.5W que provoca que el transistor se recaliente y dañe, por lo tanto, no es útil para la aplicación que se necesita darle.

|        | V <sub>CE(Sat)</sub> [V] | I <sub>MinCarga</sub> [mA] | P <sub>Max</sub> [W] | P <sub>Consumida</sub> [W] |

|--------|--------------------------|----------------------------|----------------------|----------------------------|

| 2N2222 | 1.6                      | 400                        | 0.5                  | 0.64                       |

| TIP31  | 1.2                      | 400                        | 40                   | 0.48                       |

Tabla 3.1 Comparación de transistores 2n222 y TIP31

El consumo de potencia de la carga con el TIP31 es de 0.48W que va de sobra con respecto a su potencia máxima de 40W y se adapta a los requerimientos del circuito de la Figura 3.8.

Otro elemento del sistema de medición que se debe controlar es la electroválvula, y, ya que esta también necesita únicamente de activación y apagado se usa el mismo esquema, con la diferencia de que la electroválvula necesita un voltaje de 12V para funcionar. Por esa razón el esquema electrónico es el siguiente.

Figura 3.11 Esquema electrónico de conexión de la Electroválvula

## Diseño se interfaz electrónica para bomba peristáltica

El siguiente desafío es el control de las bombas peristálticas que serán usadas para encaminar los líquidos, en su dosificación de volumen correcta, al recipiente que contendrá la solución homogénea, es decir contendrá la muestra mezclada con los solutos. La bomba peristáltica opera a 12V y 100mA, por lo que será necesario hacer el diseño de un circuito que permita elevar el nivel de corriente y a su vez opere en frecuencias con valores alrededor de 2kHz y 4kHz, ya que se planea realizar un control mediante PWM.

Figura 3.12 Esquema electrónico para el control de una Bomba peristáltica

Una señal PWM es la que permite el accionar de la bomba en un constante switcheo, permitiendo controlar su velocidad y en consecuencia controlar el flujo de líquido que pasa a través de ella. Para el uso de PWM es necesario un

elemento de conmutación rápida electrónico y en el mercado se puede encontrar un sin número de transistores útiles, uno de ellos es el 2n2222.

El uso de un solo transistor no es suficiente para accionar la carga (bomba peristáltica), la bomba opera con 12VDC y corriente de 100mA demandando una potencia de 1.2W, por ello es necesario de un transistor de potencia que permita elevar al nivel de voltaje necesario para el correcto funcionamiento de la bomba. El transistor elegido es el mosfet IRF640, el cual es un transistor de potencia capaz de manejar corrientes de 16 A y tiene una potencia de disipación de hasta 150W. Al ponerlo en cascada conectando la compuerta al colector se cumple con la etapa de potencia necesaria para el accionar de la bomba. La configuración es correcta ya que el voltaje típico de compuerta ( $V_{GS}$ ) es 3V, que es el nivel de tensión entregado por la FPGA.

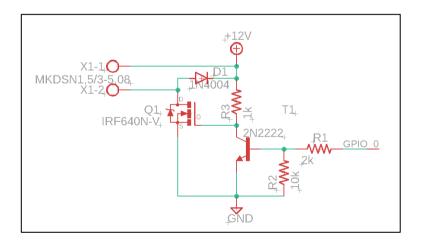

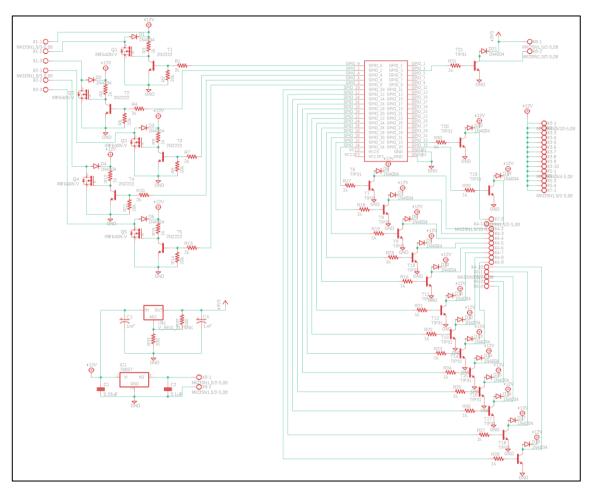

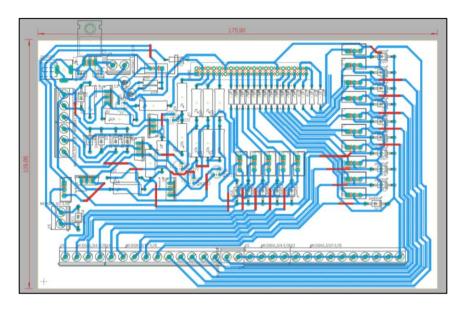

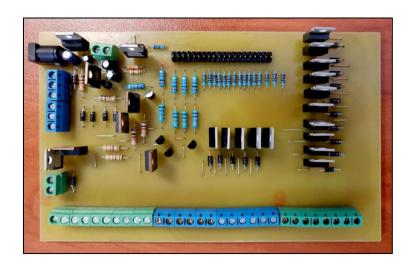

### Diseño completo de interfaces electrónicas

El esquema con todos los circuitos que controlan los actuadores que manejara el dispositivo experimental se ve reflejado en la Figura 3.13 que fue realizado en la plataforma Eagle que permite realizar el diseño de circuitos electrónicos y PCB.

Figura 3.13 Esquema completo para el manejo de periféricos en EAGLE

# 3.4. Diseño del sistema digital programado en Quartus para la interconexión entre el FPGA y el sistema operativo del mismo.

Para controlar los dispositivos a través de las interfaces electrónicas previamente diseñadas, se necesita de un sistema o circuito digital programado dentro del FPGA, que sirva como interfaz de conexión entre lo electrónico y el procesador del sistema operativo, para que de esta forma el Sistema Operativo pueda procesar los datos.

Las tarjetas de desarrollo FPGA de interés para este proyecto tienen su arquitectura dividida en dos partes esenciales. La primera dedicada al desarrollo de sistemas digitales programables llamada FPGA y la segunda dedicada a procesamiento fuerte de datos llamada HPS. En esta última es donde se encuentra el Sistema Operativo. Estas dos partes no comparten una interconexión lógica directa, así que debe ser programada dentro del FPGA e

informarle al Sistema Operativo de dichas conexiones, las cuales son llamadas Puentes/Bridges.

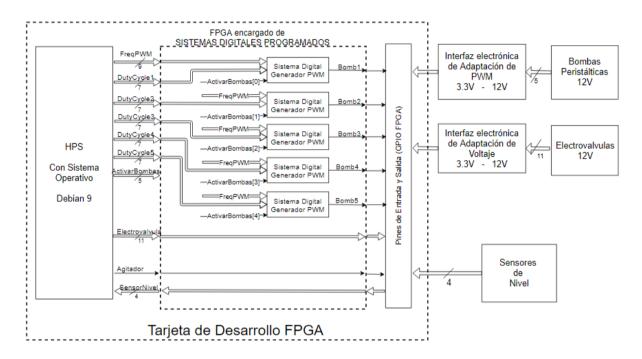

Las entradas y salidas Físicas de la FPGA no se encuentran directamente conectadas al HPS, esto se debe a que los datos se deben primero procesar en un sistema digital y solo el resultado final llegar al Sistema Operativo por esas razones, el diagrama de bloques de conexión total esperado para el controlador del dispositivo de medición de nitritos se muestra a continuación:

Figura 3.14 Diagrama de Bloques del sistema controlador.

Usando el software de Intel llamado QUARTUS PRIME, en conjunto con lenguajes de programación usados para descripción de hardware, como VHDL y verilog, se describen las conexiones y bloques contenidos en el bloque **Tarjeta de Desarrollo FPGA**, mientras que lo contenido en el bloque HPS y sus conexiones se realizan en la herramienta **Platform Designer** de QUARTUS usada para inicializar el HPS y sus conexiones externas, llamadas puentes (bridges).

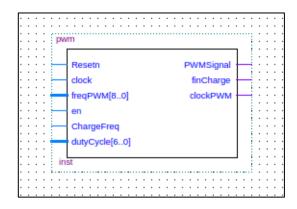

### 3.4.1. Bloque Generador de PWM

Este bloque se encarga de generar la señal PWM para el control de las bombas peristálticas, y, es un sistema digital sincrónico, es decir, depende de un clock. Ya que, gracias a este puede realizar la cuenta de la cantidad de pulsos de reloj

necesarios para obtener la frecuencia y el Duty Cycle deseado en la salida PWM. Dentro de este bloque se realiza una división entre el clock de entrada y la frecuencia de clock deseada para el PWM para obtener la cantidad de pulsos del clock de entrada que se deben contar para cambiar de estado el clock del PWM. Las señales que este bloque usa se listan a continuación:

- Resetn: Al activar esta señal todas las salidas del Generador PWM son apagadas.

- Clock: Al ser un circuito secuencial usa un clock como una señal que determina el instante en que se debe realizar un cambio.

- FreqPWM[8..0]: A través de esta señal de 9 bits se indica al sistema la frecuencia deseada para el PWM.

- En: Mediante esta señal, se activa la señal PWM en la salida PWMSignal.

Si "en" no está activa entonces la señal PWM es apagada.

- ChargeFreq: Usando esta señal se indica al sistema que debe realizar las operaciones necesarias para cambiar la frecuencia del PWM a la frecuencia presente en la señal "FreqPWM[8..0]". El fin de esta operación es indicado por la salida "finCharge".

- DutyCycle[6..0]: En esta señal de 9 bits se indica el Duty Cycle deseado para la señal PWM.

- PWMSignal: En esta salida está presente la señal PWM que controla las bombas.

- FinCharge: Esta señal indica el fin de la operación de carga de frecuencia, como se indicó anteriormente.

- ClockPWM: Esta señal de salida tiene el clock con el que el PWM realiza la cuenta para el Duty Cycle, es decir, 100 pulsos de este reloj es un ciclo del PWM. Entonces, por ejemplo, si se desea obtener un Duty Cycle del 70% se mantendra encendida "PWMSignal" durante 70 pulsos del reloj "ClockPWM" y los restantes 30 pulsos se deberá apagar dicha señal.

El diagrama de entradas y salidas del bloque descrito se muestra a continuación:

Figura 3.15 Diagrama de entradas y salidas del bloque generador de PWM.

Izquierda entradas y Derecha salidas

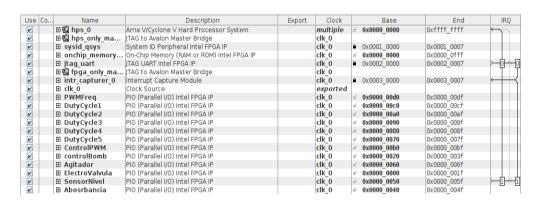

#### 3.4.2. Instanciación HPS

La instanciación del HPS se realiza en el Platform Designer de Quartus en el cual también se definen las memorias, puertos y bridges que el sistema tendrá; todo esto queda almacenado en un archivo "Qsys". En la imagen a continuación se muestra un resumen del sistema diseñado para el presente proyecto.

Figura 3.16 Resumen del Sistema Qsys del controlador

En el diagrama presentado en la figura anterior se muestran los elementos del sistema y su rango de direcciones ubicado entre Base y End, las cuales son direcciones de memoria usadas para que el sistema operativo del HPS pueda acceder y controlar los bridges necesarios. Los elementos usados en este sistema se listan a continuación:

Hps\_0: este es el procesador o el núcleo del sistema, que, como se ve en descripción es un procesador Cyclone V. Se decidió elegir entre este tipo de procesadores, puesto que, las tarjetas que incluyen procesadores más potentes como el Arria 10 y el Stratix 10 tienen un precio elevado y sobre exceden lo necesario para este proyecto. Las diferencias entre estos procesadores se listan en la tabla a continuación.

| HPS Module                                            | Cyclone V SoC                                                                                | Arria V SoC                                                                                  | Arria 10 SoC                                                                                 | Stratix 10 SoC                                                |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Microprocessor Unit Subsystem (MPU)                   | Single / Dual<br>Cortex®-A9                                                                  | Dual Cortex-A9                                                                               | Dual Cortex-A9                                                                               | Quad Cortex-<br>A53                                           |

| Cache Coherency Controller                            | Accelerator<br>coherency port<br>(ACP)                                                       | ACP                                                                                          | ACP                                                                                          | Cache<br>Coherency Unit<br>(CCU)                              |

| System Memory Management Unit                         | No                                                                                           | No No                                                                                        |                                                                                              | Yes                                                           |

| On-Chip RAM                                           | 64 KB                                                                                        | 64 KB                                                                                        | 256 KB                                                                                       | 256 KB                                                        |

| Error Correction Code (ECC) Controller                | No                                                                                           | No                                                                                           | Yes                                                                                          | Yes                                                           |

| HPS-FPGA Bridges                                      | Yes                                                                                          | Yes                                                                                          | Yes                                                                                          | Yes                                                           |

| General Purpose I/O (GPIO)                            | Yes                                                                                          | Yes                                                                                          | Yes                                                                                          | Yes                                                           |

| Available dedicated I/Os                              | 10                                                                                           | 10                                                                                           | 17                                                                                           | 48                                                            |

| Available shared I/Os                                 | Up to 67                                                                                     | 94                                                                                           | 48                                                                                           | 0                                                             |

| SDRAM Controller                                      | Inside HPS                                                                                   | Inside HPS                                                                                   | Outside of HPS                                                                               | Outside of HPS                                                |

| NAND Flash Controller                                 | Yes                                                                                          | Yes                                                                                          | Yes                                                                                          | Yes                                                           |

| Secure digital/multimedia card (SD/MMC)<br>Controller | Yes                                                                                          | Yes                                                                                          | Yes                                                                                          | Yes                                                           |

| MPU Subsystem Feature                                 | Cyclone V SoC                                                                                | Arria V SoC                                                                                  | Arria 10 SoC                                                                                 | Stratix 10 SoC                                                |

| CPU                                                   | Single/Dual<br>Cortex-A9                                                                     | Dual Cortex-A9                                                                               | Dual Cortex-A9                                                                               | Quad Cortex-<br>A53                                           |

| Maximum frequency (MHz)                               | 925                                                                                          | 1050                                                                                         | 1500                                                                                         | 1500                                                          |

| Core revision                                         | r3p0                                                                                         | r3p0                                                                                         | r4p1-00rel0                                                                                  | r0p4-51rel0                                                   |

| L1 instruction cache                                  | 32 KB                                                                                        | 32 KB                                                                                        | 32 KB                                                                                        | 32 KB                                                         |

| L1 data cache                                         | 32 KB                                                                                        | 32 KB                                                                                        | 32 KB                                                                                        | 32 KB                                                         |

| L2 cache                                              | 512 KB                                                                                       | 512 KB                                                                                       | 512 KB                                                                                       | 1 MB                                                          |

| ACP enabled                                           | Yes                                                                                          | Yes                                                                                          | Yes                                                                                          | No <sup>(2)</sup>                                             |

| L1 data cache error checking                          | Parity (3)                                                                                   | Parity <sup>(3)</sup>                                                                        | Parity <sup>(3)</sup>                                                                        | ECC (4)                                                       |

| L1 instruction cache error checking                   | Parity <sup>(3)</sup>                                                                        | Parity <sup>(3)</sup>                                                                        | Parity <sup>(3)</sup>                                                                        | Parity <sup>(3)</sup> on<br>data and tag<br>bits              |

| L2 cache error checking                               | ECC <sup>(5)</sup> ; ECC<br>interrupts;<br>optional<br>parity <sup>(3)</sup> for tag<br>bits | ECC <sup>(5)</sup> ; ECC<br>interrupts;<br>optional<br>parity <sup>(3)</sup> for<br>tag bits | ECC <sup>(5)</sup> ; ECC<br>interrupts;<br>optional<br>parity <sup>(3)</sup> for<br>tag bits | ECC <sup>(5)</sup> on data<br>and tag bits;<br>ECC interrupts |

|                                                       |                                                                                              |                                                                                              |                                                                                              |                                                               |

Figura 3.17 Diferencias entre Hard Processors usados en SOC FPGA's [15]

- Hps\_only\_master: este es un puente entre el puerto JTAG, usada para la carga del programa FPGA, y el sistema operativo.

- SySid\_qsys: Bloque que asigna un id de identificación al sistema, y, siempre es requerido.

- Onchip\_memory: Bloque de memoria usado para asignar RAM al sistema operativo.

- Jtag\_uart: Activa el puerto UART para la comunicación del sistema operativo con un Host PC, esto permite realizar la configuración inicial del OS.

- Fpga\_only\_master: este es un puente entre el puerto JTAG de la FPGA y el sistema de memoria del HPS.

- Intr\_capturer: Encargado de capturar las interrupciones que los demás bloques realicen.

- Clk\_0: Fuente de reloj de 5MHz, basándose en el clock del HPS, el cual es de 50 MHz.

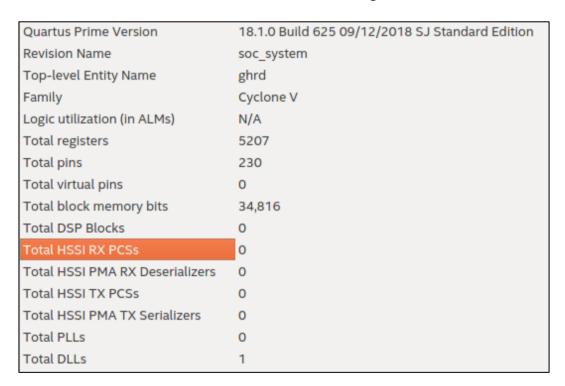

- PIO (Parallel Input/Output): Bridges creados para comunicar el sistema operativo con el sistema digital.